MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-15

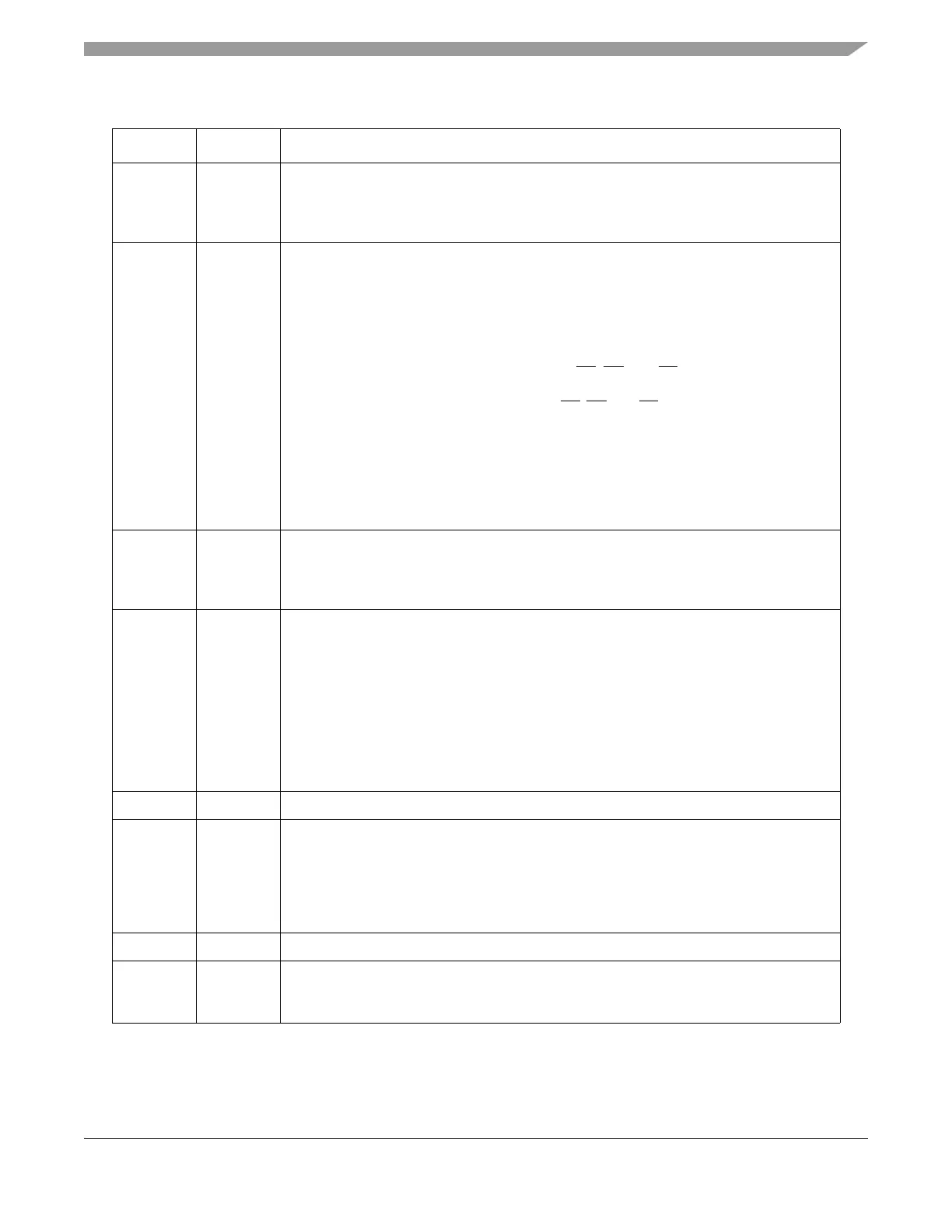

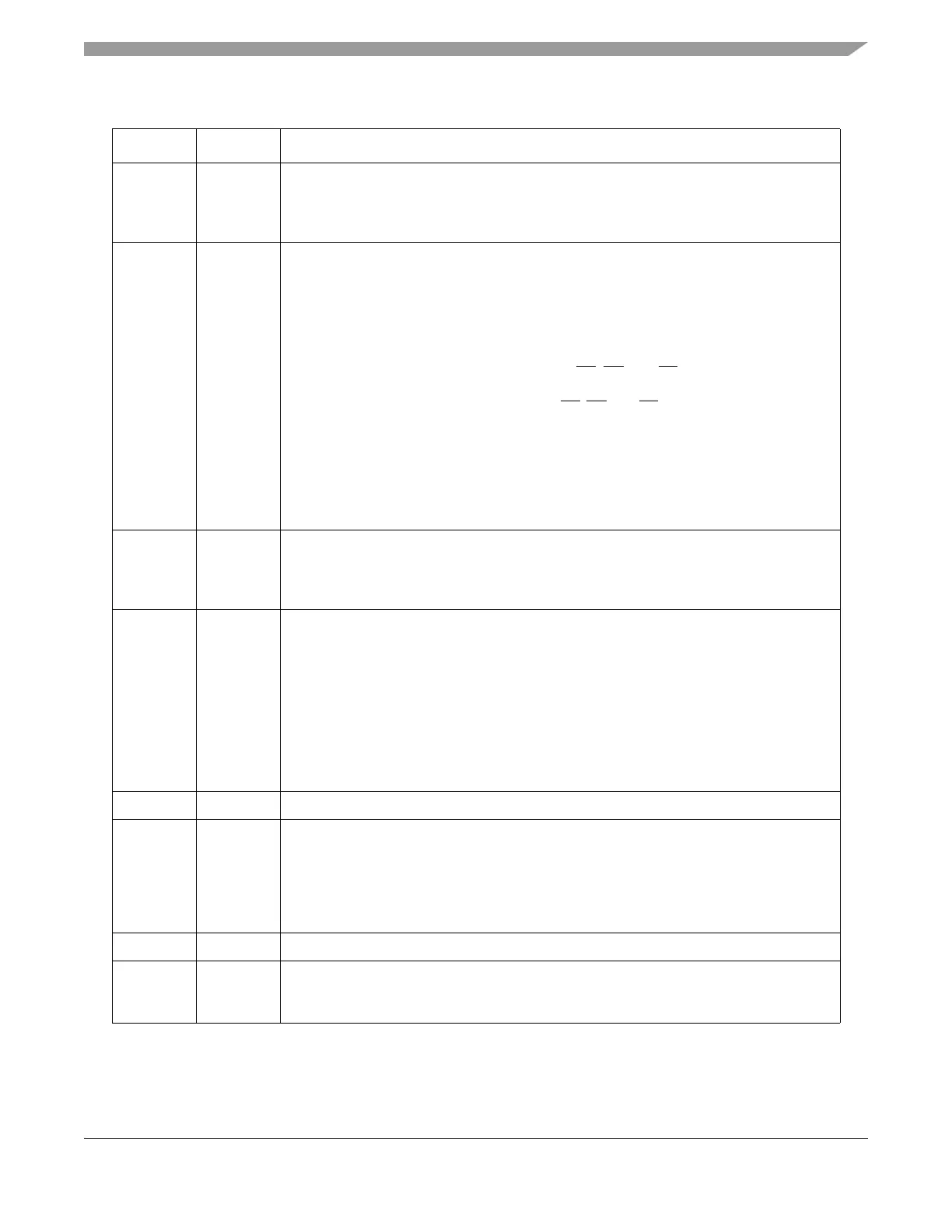

16 ACGE Automatic CLKOUT gating enable. Enables the EBI feature of turning off CLKOUT (holding

it high) during idle periods in-between external bus accesses.

0 Automatic CLKOUT gating is disabled

1 Automatic CLKOUT gating is enabled

17 EXTM External master mode. Enables the external master mode of operation when MDIS = 0.

When MDIS = 1, the EXTM bit is a don’t care, and is treated as 0. In external master mode,

an external master on the external bus can access any internal memory-mapped space

while the internal e200z6 core is fully operational.

Single master mode (EXTM = 0) only allows internal masters to access internal memory.

This bit also determines the functionality of the BR

, BG, and BB signals.

Note: The SIU PCR registers must configure BR

, BG, and BB for EBI function (as opposed

to default GPIO) prior to EXTM being set to 1, or erroneous behavior may result.

0 External master mode is inactive (single master mode)

1 External master mode is active

Note: In the MPC5553, only master/slave systems support the EXTM functionality. Refer

to Section 12.5.5, “Dual-MCU Operation with Reduced Pinout MCUs.“

18 EARB External arbitration. See Section 12.4.2.8, “Arbitration,” for details on internal and external

arbitration. When EXTM = 0, the EARB bit is a don’t care, and is treated as 0.

0 Internal arbitration is used.

1 External arbitration is used.

19–20 EARP

[0:1]

External arbitration request priority. Defines the priority of an external master’s arbitration

request (0–2), with 2 being the highest priority level (EARP = 3 is reserved). This field is

valid only when EARB = 0 (internal arbitration). The internal masters of the MCU have a

fixed priority of 1. By default, internal and external masters have equal priority. See

Section 12.4.2.8.2, “Internal Bus Arbiter,” for the internal and external priority detailed

description.

00 MCU has priority

01 Equal priority, round robin used

10 External master has priority

11 Reserved

21–24 — Reserved.

25 MDIS Module disable mode. Allows the clock to be stopped to the non-memory mapped logic in

the EBI, effectively putting the EBI in a software controlled power-saving state. See

Section 12.1.4.3, “Module Disable Mode,” for more information. No external bus accesses

can be performed when the EBI is in module disable mode (MDIS = 1).

0 Module disable mode is inactive

1 Module disable mode is active

26–30 — Reserved.

31 DBM Data bus mode. Controls whether the EBI is in 32-bit or 16-bit data bus mode.

0 32-bit data bus mode is used

1 16-bit data bus mode is used

Table 12-7. EBI_MCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...