MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

12-16 Freescale Semiconductor

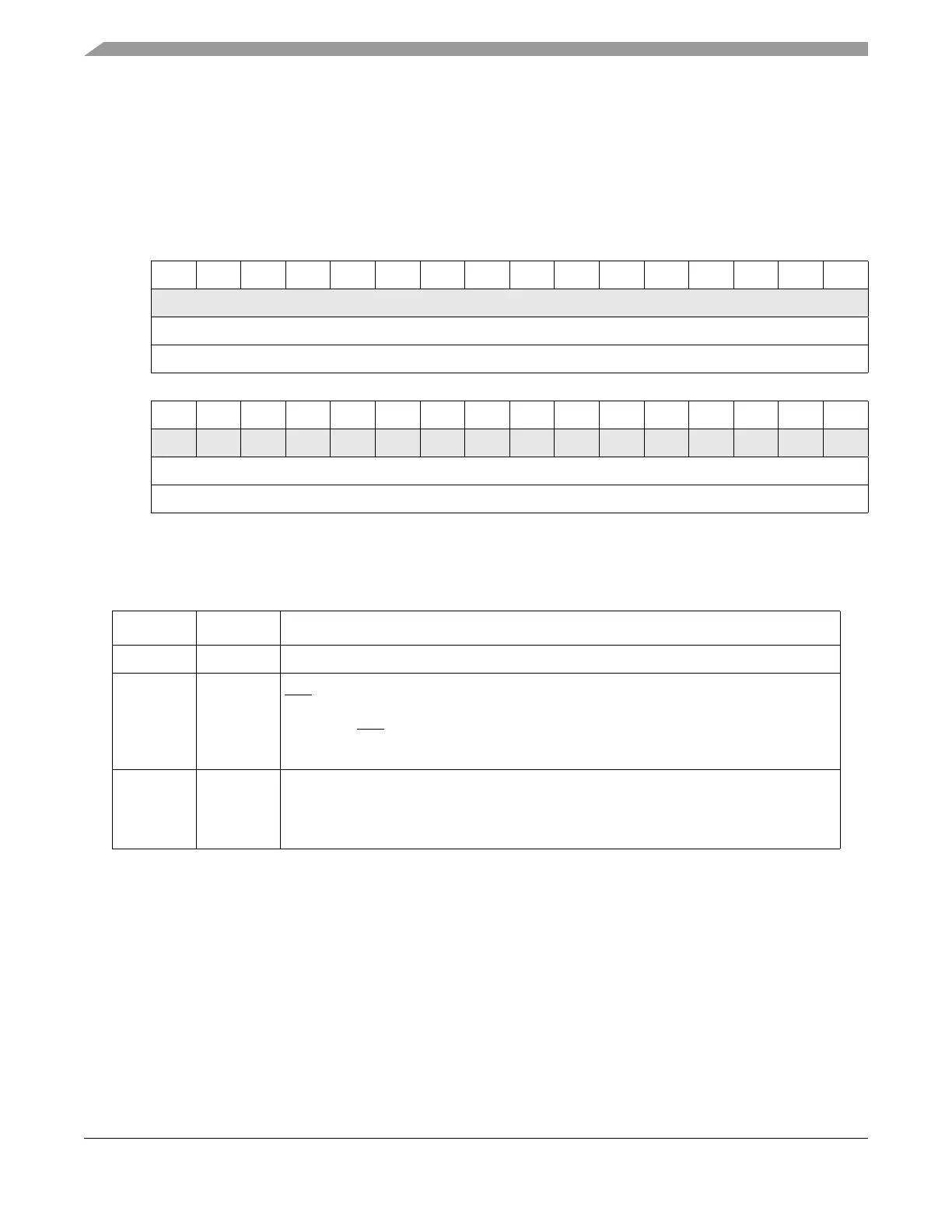

12.3.1.4 EBI Transfer Error Status Register (EBI_TESR)

The EBI_TESR contains a bit for each type of transfer error on the external bus. A bit set to logic 1

indicates what type of transfer error occurred because the last time the bits were cleared. Each bit can be

cleared by reset or by writing a 1 to it. Writing a 0 has no effect.

This register is not writable in module disable mode due to the use of power saving clock modes.

12.3.1.5 EBI Bus Monitor Control Register (EBI_BMCR)

The EBI_BMCR controls the timeout period of the bus monitor and whether it is enabled or disabled.

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x0008

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000000000TEAFBMTF

W w1c w1c

Reset0000000000000000

Reg Addr Base + 0x0008

Note: w1c means “write 1 to clear.”

Figure 12-3. EBI Transfer Error Status Register (EBI_TESR)

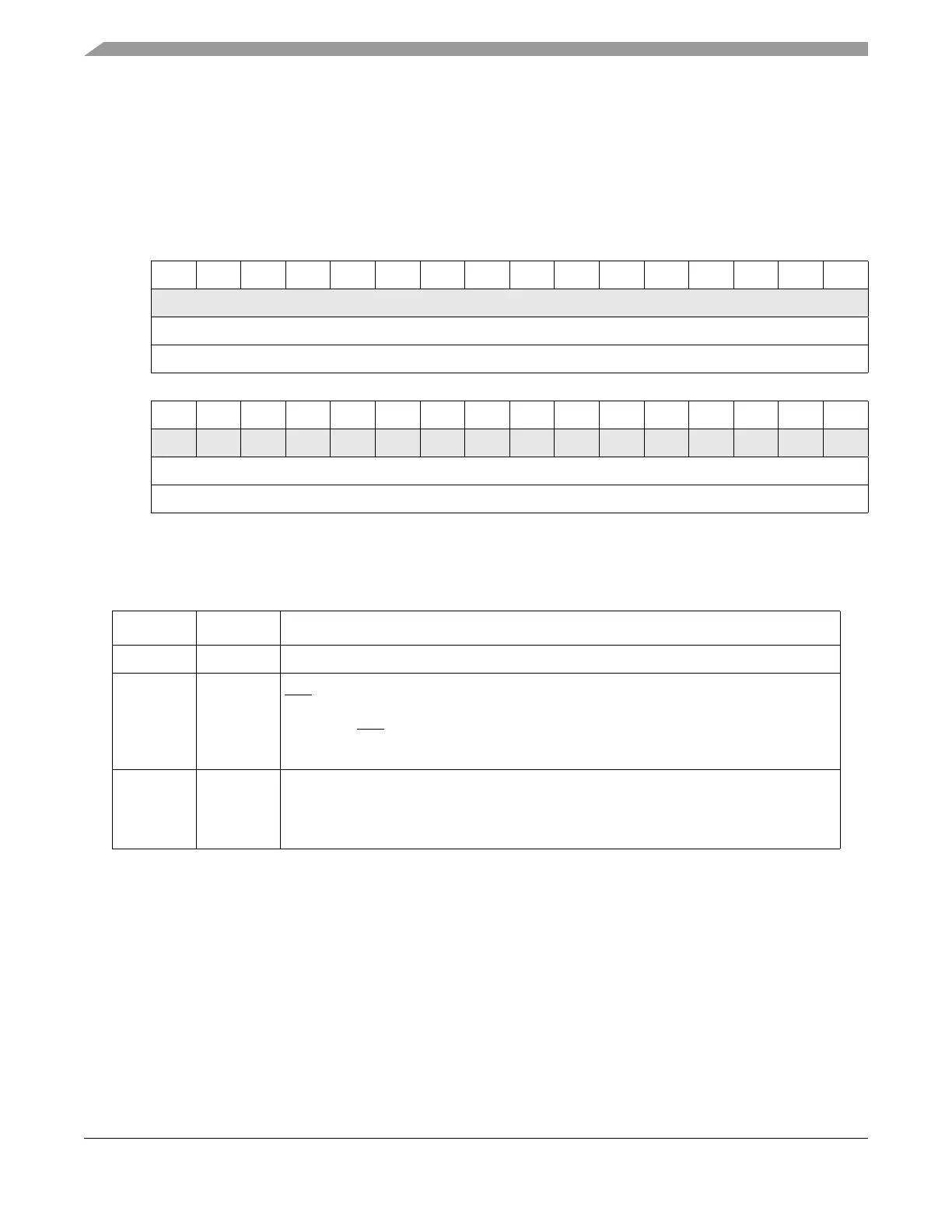

Table 12-8. EBI_TESR Field Descriptions

Bits Name Description

0–29 — Reserved.

30 TEAF Transfer error acknowledge flag. Set if the cycle was terminated by an externally generated

TEA

signal.

0 No error

1 External TEA occurred

This bit can be cleared by writing a 1 to it.

31 BMTF Bus monitor timeout flag. Set if the cycle was terminated by a bus monitor timeout.

0 No error

1 Bus monitor timeout occurred

This bit can be cleared by writing a 1 to it.

Loading...

Loading...