MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-17

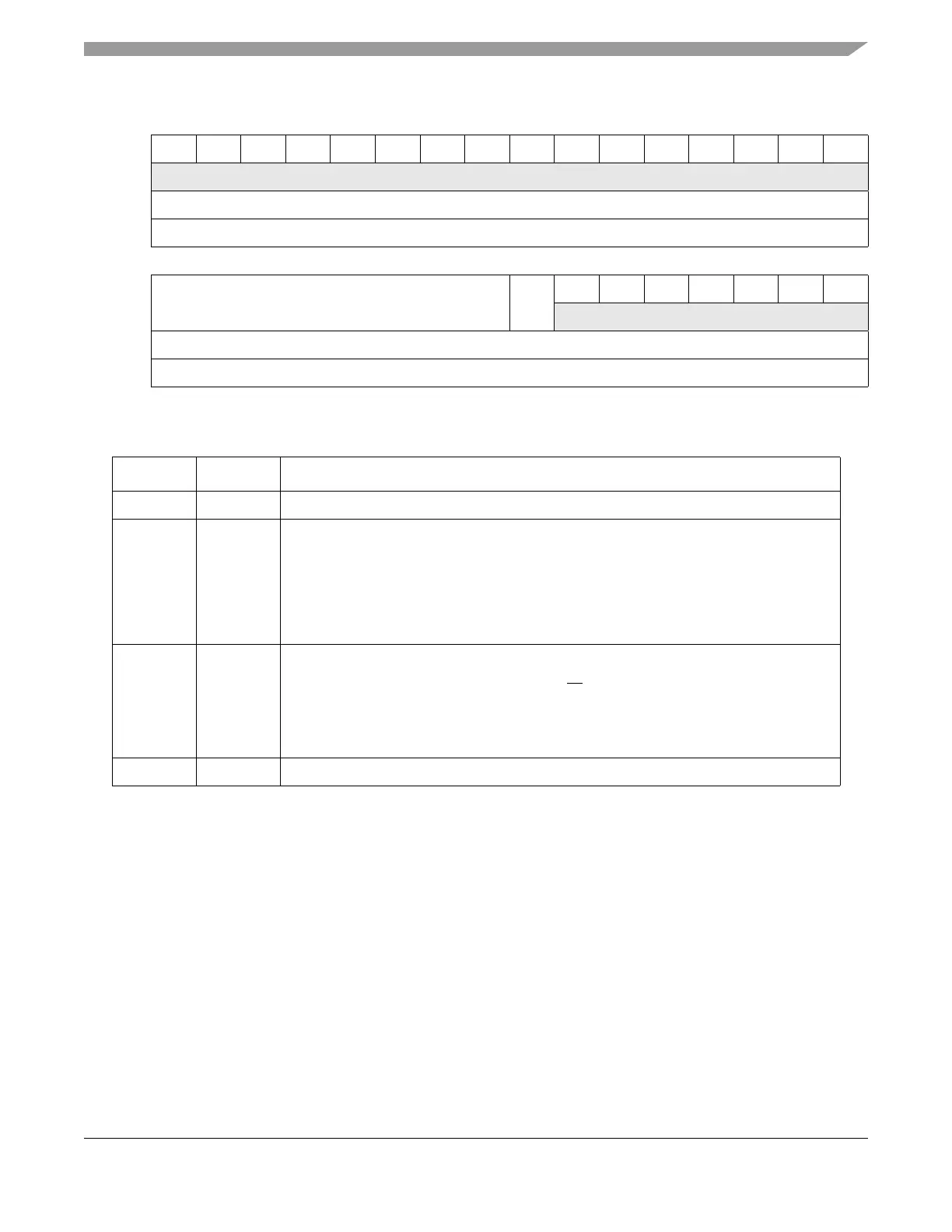

12.3.1.6 EBI Base Registers 0–3 (EBI_BRn) and EBI Calibration Base Registers

0–3 (EBI_CAL_BRn)

The EBI_BRn are used to define the base address and other attributes for the corresponding chip select.

The EBI_CAL_BRn appear in the MPC5553 only and are used to define the base address and other

attributes for the corresponding calibration chip select.

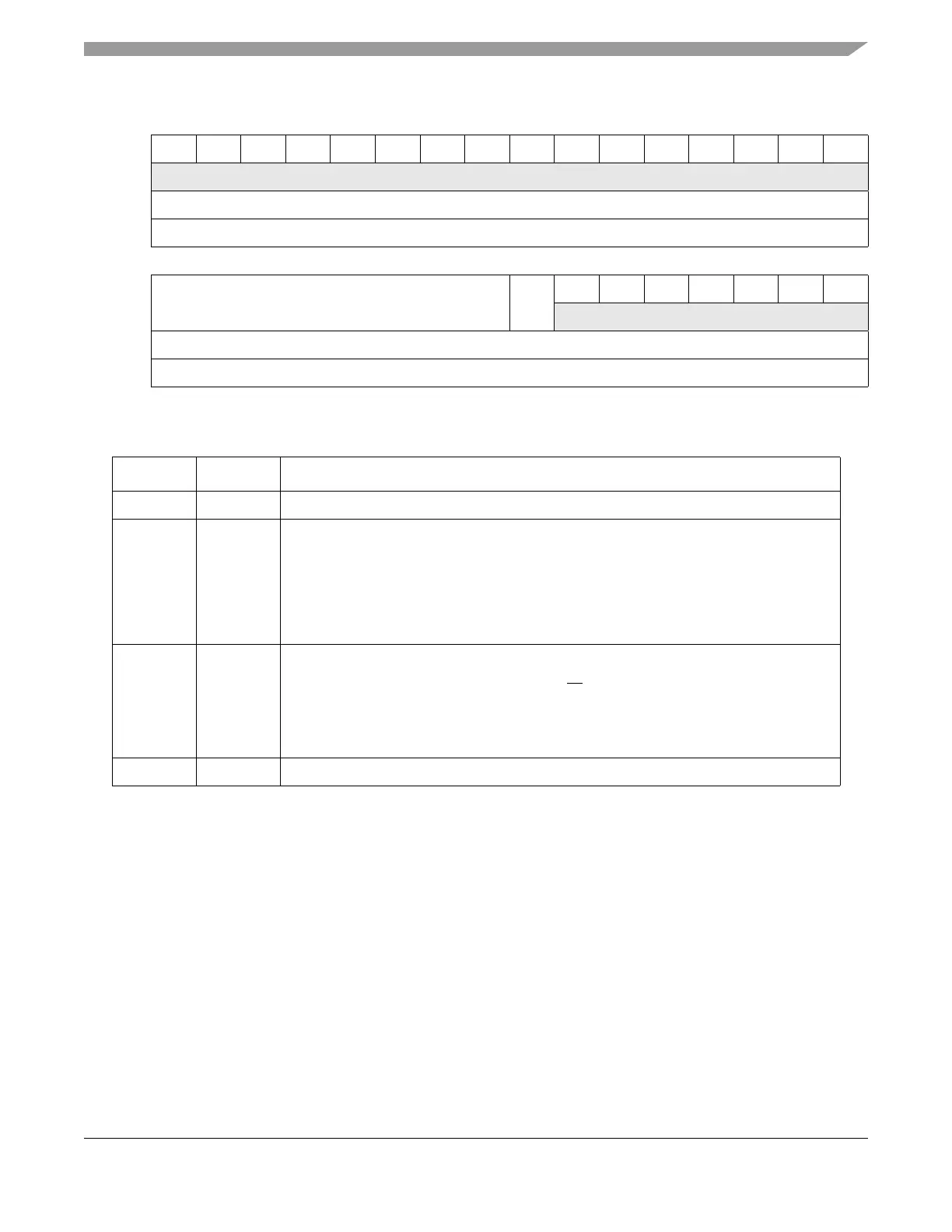

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x000C

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R BMT BME0000000

W

Reset1111111110000000

Reg Addr Base + 0x000C

Figure 12-4. EBI Bus Monitor Control Register (EBI_BMCR)

Table 12-9. EBI_BMCR Field Descriptions

Bits Name Description

0–15 — Reserved.

16–23 BMT

[0:7]

Bus monitor timing. Defines the timeout period, in 8 external bus clock resolution, for the

Bus Monitor. See Section 12.4.1.7, “Bus Monitor,” for more details on bus monitor

operation.

24 BME Bus monitor enable. Controls whether the bus monitor is enabled for internal to external

bus cycles. Regardless of the BME value, the bus monitor is always disabled for chip select

accesses, because these always use internal TA

and thus have no danger of hanging the

system.

0 Disable bus monitor

1 Enable bus monitor (for non-chip select accesses only)

25–31 — Reserved.

Timeout Period

2 + (8 BMT)

External Bus Clock Frequency

--------------------------------------------------------------------------------=

Loading...

Loading...