MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-45

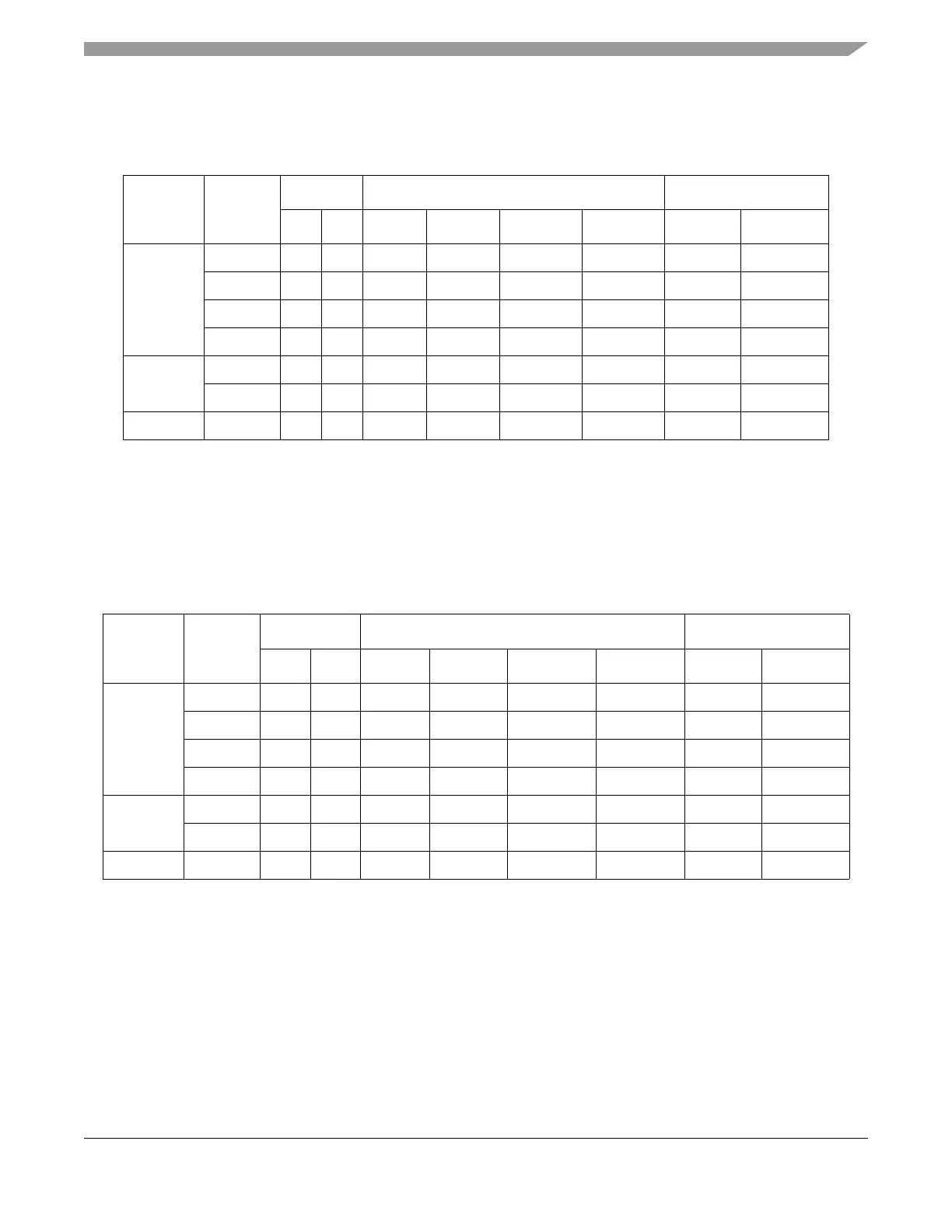

Table 12-19 lists the bytes required on the data bus for read cycles. The bytes indicated as ‘—’ are not

required during that read cycle.

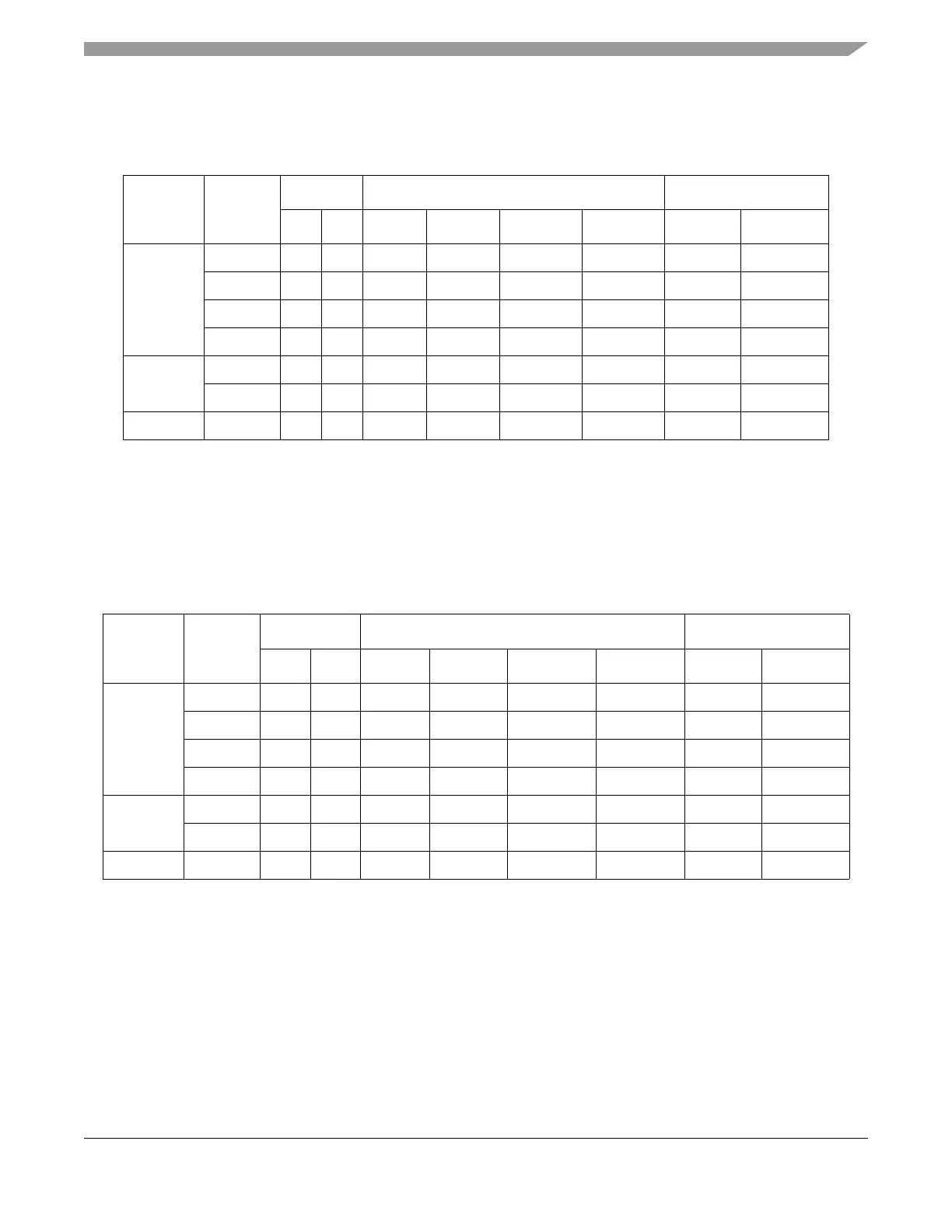

Table 12-20 lists the patterns of the data transfer for write cycles when accesses are initiated by the MCU.

The bytes indicated as ‘—’ are indeterminate and may be driven during that write cycle.

12.4.2.8 Arbitration

The external bus design provides for a single bus master at any one time, either the MCU or an external

device. One of the external devices on the bus has the capability of becoming bus master for the external

bus. Bus arbitration may be handled either by an external central bus arbiter or by the internal on-chip

arbiter. The arbitration configuration (external or internal) is set via the EARB bit in the EBI_MCR.

Table 12-19. Data Bus Requirements for Read Cycles

Transfer

Size

TSIZ[0:1]

1

1

TSIZ is not enabled on the MPC5553.

Address 32-Bit Port Size 16-Bit Port Size

2

2

Also applies when DBM=1 for 16-bit data bus mode.

A30 A31 D0:D7 D8:D15 D16:D23 D24:D31 D0:D7 D8:D15

Byte 01 0 0 OP0 — — — OP0 —

01 0 1 — OP1 — — — OP1

01 1 0 — — OP2 — OP2 —

01 1 1 — — — OP3 — OP3

16-bit 10 0 0 OP0 OP1 — — OP0 OP1

10 1 0 — — OP2 OP3 OP2 OP3

32-bit 00 0 0 OP0 OP1 OP2 OP3 OP0/OP2

3

3

This case consists of two 16-bit external transactions, the first fetching OP0 and OP1, the second fetching OP2

and OP3.

OP1/OP3

Table 12-20. Data Bus Contents for Write Cycles

Transfer

Size

TSIZ[0:1]

1

1

TSIZ is not enabled on the MPC5553.

Address 32-Bit Port Size 16-Bit Port Size

2

2

Also applies when DBM=1 for 16-bit data bus mode.

A30 A31 D0:D7 D8:D15 D16:D23 D24:D31 D0:D7 D8:D15

Byte 01 0 0 OP0 — — — OP0 —

01 0 1 — OP1 — — — OP1

01 1 0 — — OP2 — OP2 —

01 1 1 — — — OP3 — OP3

16-bit 10 0 0 OP0 OP1 — — OP0 OP1

10 1 0 — — OP2 OP3 OP2 OP3

32-bit 00 0 0 OP0 OP1 OP2 OP3 OP0/OP2

3

3

This case consists of two 16-bit external transactions, the first writing OP0 and OP1, the second writing OP2 and OP3.

OP1/OP3

Loading...

Loading...