MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

12-44 Freescale Semiconductor

so a multi-master system with two MPC55xx MCUs can never have a misaligned external access. In the

erroneous case that an externally-initiated misaligned access does occur, the EBI errors the access (by

asserting TEA externally) and does not initiate the access on the internal bus.

The bus requires that the portion of the data bus used for a transfer to/from a particular port size be fixed.

A 32-bit port must reside on data bus bits 0-31, and a 16-bit port must reside on bits 0-15.

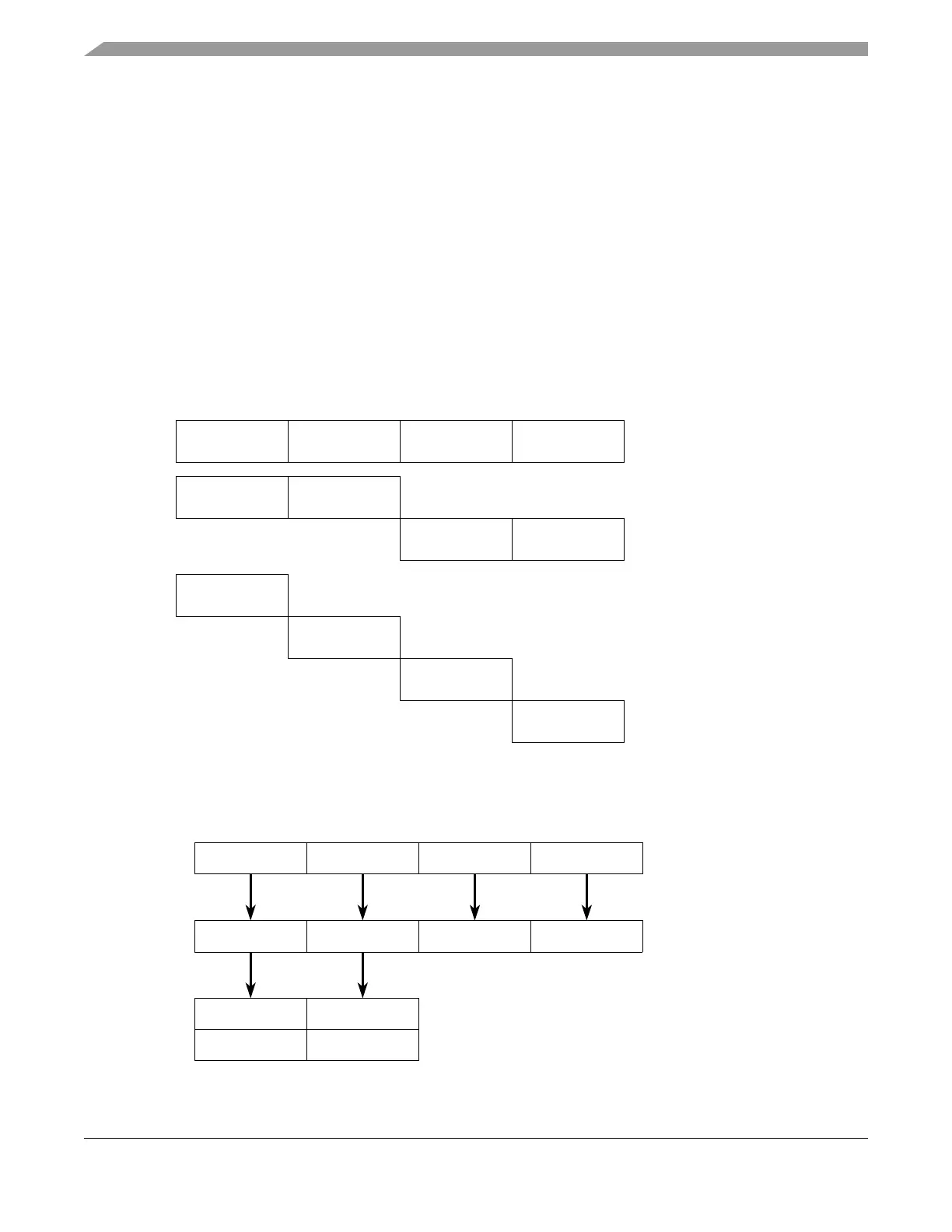

In the following figures and tables the following convention is adopted:

• The most significant byte of a 32-bit operand is OP0, and OP3 is the least significant byte.

• The two bytes of a 16-bit operand are OP0 (most significant) and OP1, or OP2 (most significant)

and OP3, depending on the address of the access.

• The single byte of a byte-length operand is OP0, OP1, OP2, or OP3, depending on the address of

the access.

The convention can be seen in Figure 12-30.

Figure 12-30. Internal Operand Representation

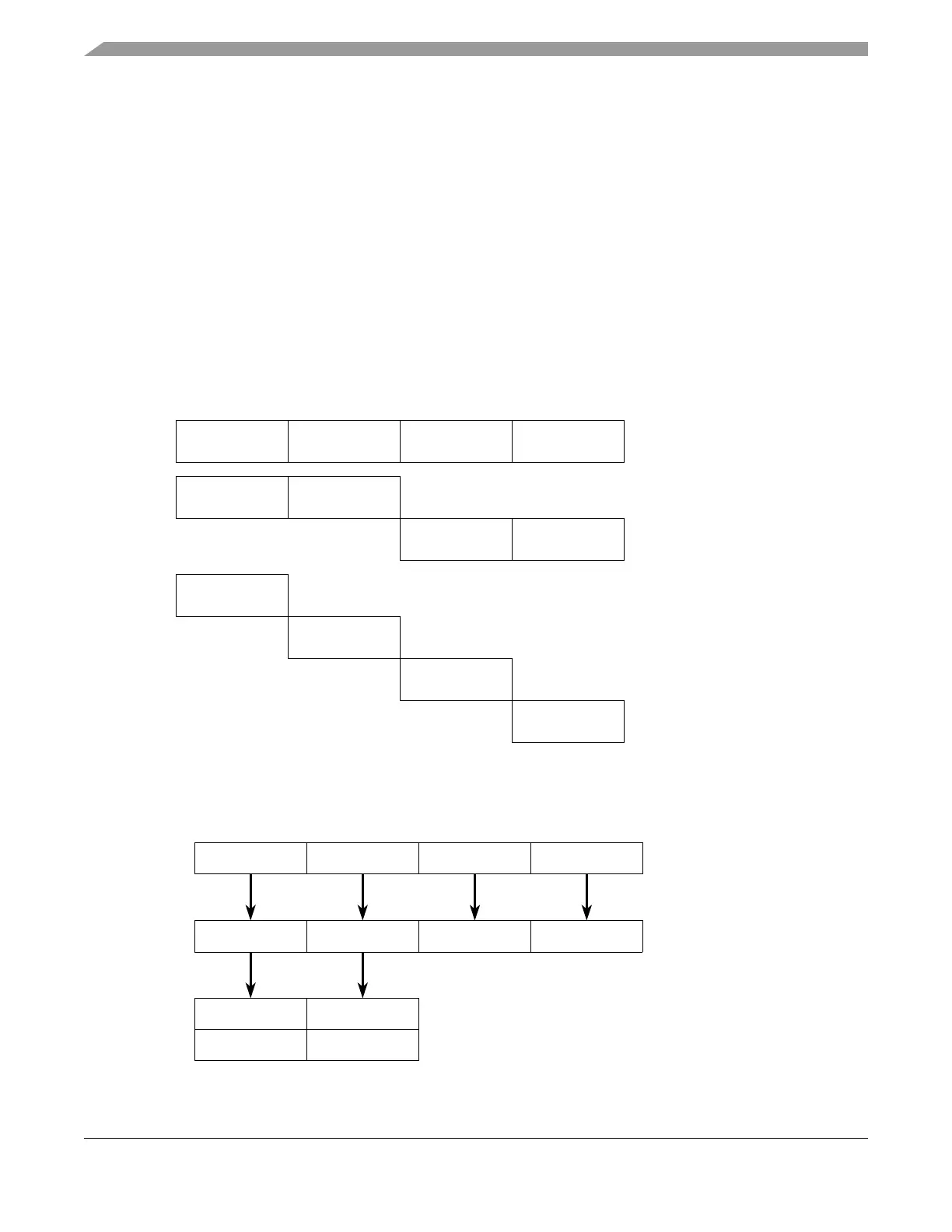

Figure 12-31 shows the device connections on the DATA[0:31] bus.

Figure 12-31. Interface to Different Port Size Devices

OP0 OP1 OP2

031

32-Bit

16-Bit

Byte

OP0

OP1

OP2

OP3

OP0 OP1

OP2 OP3

OP3

031

DATA[16:23]

32-bit Port Size

DATA[24:31]DATA[8:15]DATA[0:7]

Interface Output

Register

16-bit Port Size

OP0 OP1 OP2 OP3

OP0 OP1 OP2 OP3

OP0 OP1

OP2 OP3

Loading...

Loading...