MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-43

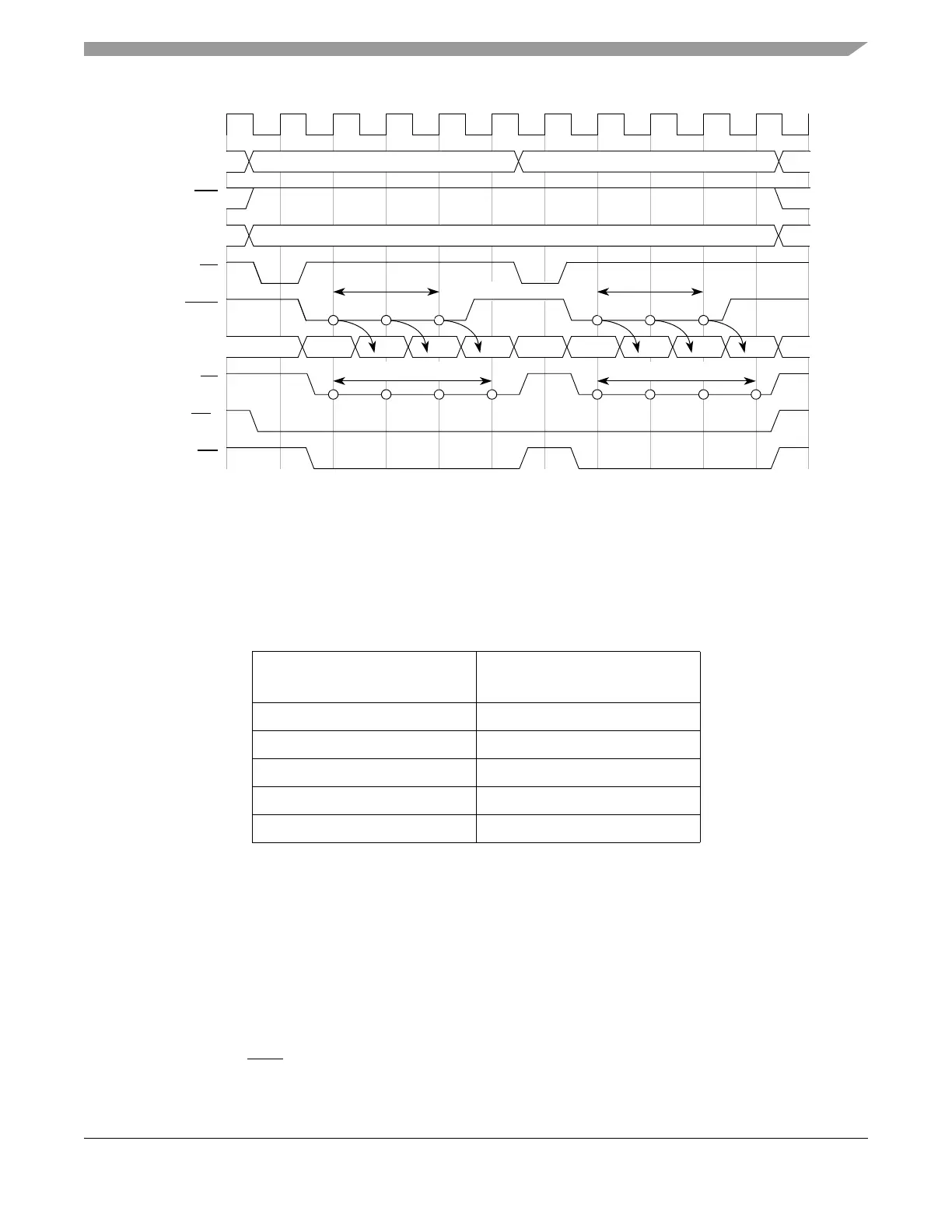

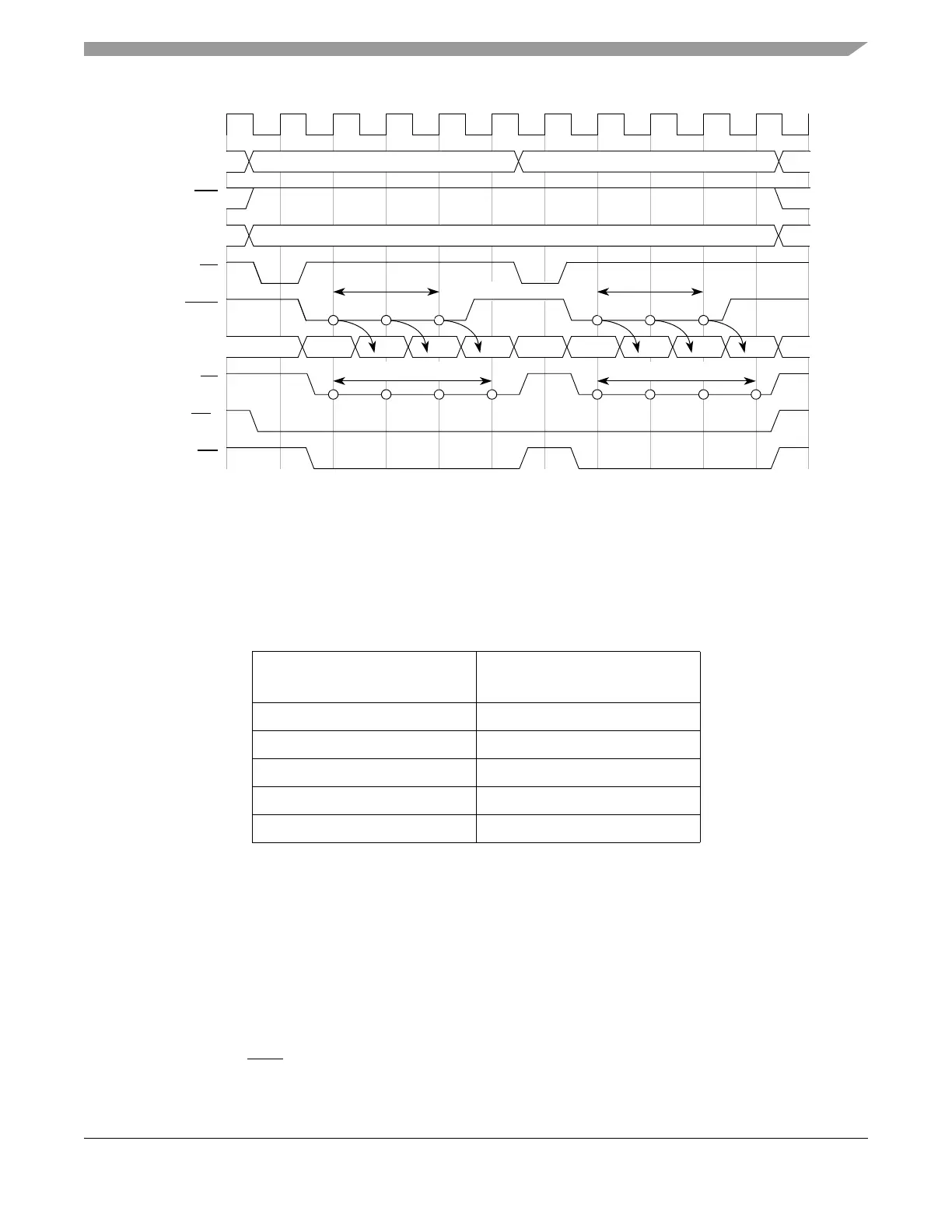

Figure 12-29. 32-Byte Read with Back-to-Back 16-Byte Bursts to 32-bit Port, Zero Wait States

12.4.2.7 Size, Alignment, and Packaging on Transfers

Table 12-18 shows the allowed sizes that an internal or external master can request from the EBI. The

behavior of the EBI for request sizes not shown below is undefined. No error signal is asserted for these

erroneous cases.

Note: Some misaligned access cases may result in 3-byte writes. These cases are treated as power-of-2 sized requests by the

EBI, using WE/BE[0:3] to make sure only the appropriate 3 bytes get written.

The EBI supports only natural address alignment:

• Byte access can have any address.

• 16-bit access, address bit 31 must be 0.

• 32-bit access, address bits 30-31 must be 0.

• For burst accesses of any size, address bits 29-31 must be 0.

The EBI of the MPC5553 and MPC5554 does not support misaligned accesses. If a misaligned access to

the EBI is attempted by an internal master, the EBI errors the access on the internal bus and does not start

the access (nor assert TEA) externally. This means the EBI never generates a misaligned external access,

Table 12-18. Transaction Sizes Supported by EBI

Number of Bytes (Internal

Master)

Number of Bytes (External

Master)

11

22

44

8

32

Expects more data

CLKOUT

ADDR[8:31]

BDIP

DATA[0:31]

TA

RD_WR

TSIZ[0:1]

TS

OE

CSx

ADDR[29:31] = ‘000’

DATA is valid

00

ADDR[28:31] = ‘0000’

DATA is valid

Loading...

Loading...