MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-25

12.4.1.15 Configurable Bus Speed Clock Modes

The EBI supports configurable bus speed clock modes. Refer to Section 12.1.4.4, “Configurable Bus

Speed Modes,” for more details on this feature.

12.4.1.16 Module Disable Mode for Power Savings

See Section 12.1.4, “Modes of Operation,” for a description of the power saving mode.

12.4.1.17 Optional Automatic CLKOUT Gating

The EBI has the ability to hold the external CLKOUT pin high when the EBI’s internal master state

machine is idle and no requests are pending. The EBI outputs a signal to the pads logic in the MCU to

disable CLKOUT. This feature is disabled out of reset, and can be enabled or disabled by the ACGE bit in

the EBI_MCR.

NOTE

This feature must be disabled for multi-master systems. In those cases, one

master is getting its clock source from the other master and needs CLKOUT

to stay valid continuously.

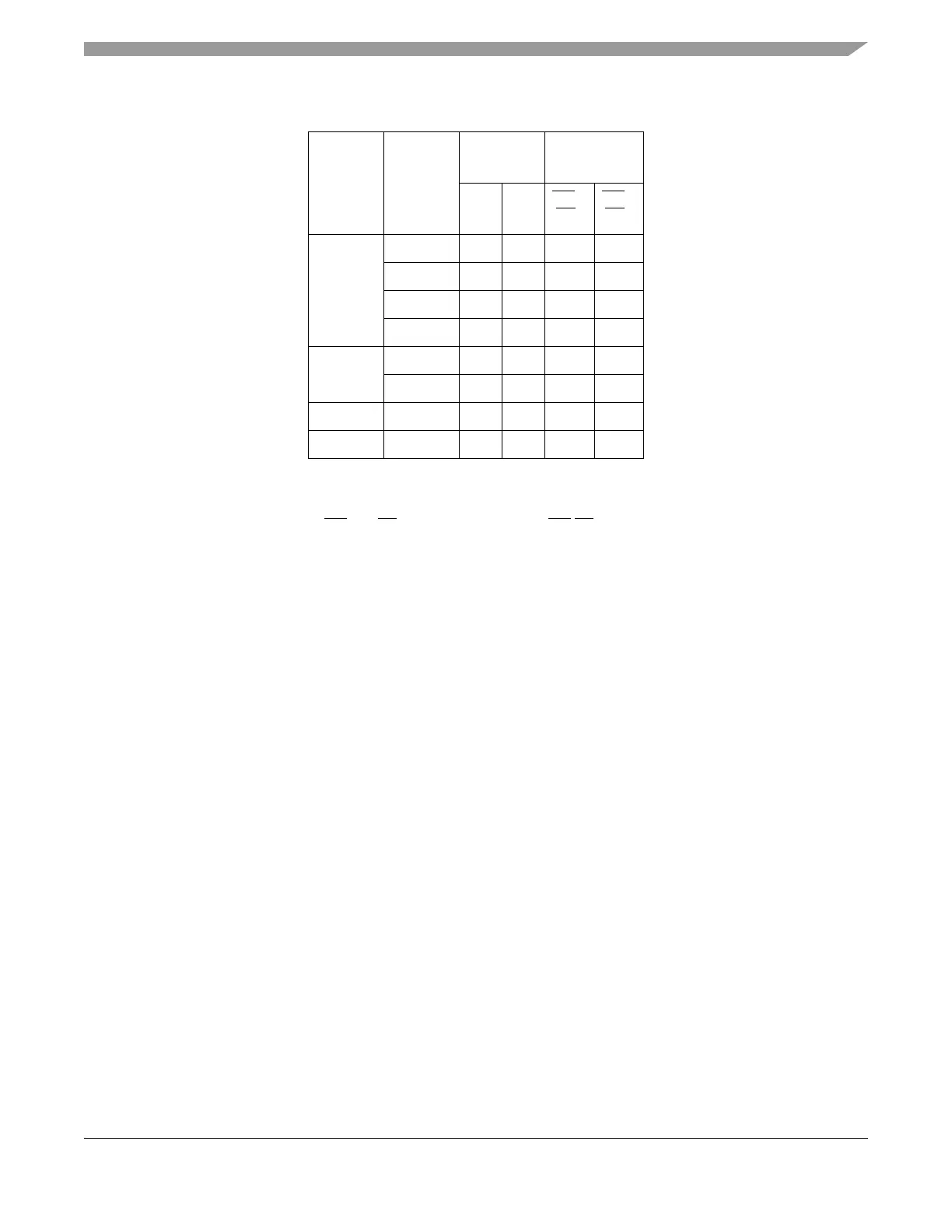

Table 12-14. Write/Byte Enable Signals Function -- 324 BGA

Transfer

Size

TSIZ[0:1]

Address

16-Bit Port

Size

1

1

Also applies when DBM=1 for 16-bit data bus mode.

A30 A31

WE

0/

BE

0

WE

1/

BE

1

Byte 01 0 0 X —

01 0 1 — X

01 1 0 X —

01 1 1 — X

16-bit 10 0 0 X X

10 1 0 X X

32-bit 00 0 0 X

2

2

This case consists of two 16-bit external

transactions, but for both transactions the

WE[0:1]/BE[0:1] signals are the only WE/BE signals

affected.

NOTE: “X” indicates that valid data is transferred on

these bits.

X

2

Burst 00 0 0 X X

Loading...

Loading...