MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

12-40 Freescale Semiconductor

12.4.2.6 Small Accesses (Small Port Size and Short Burst Length)

In this context, a small access refers to an access whose burst length and port size are such that the number

of bytes requested by the internal master cannot all be fetched (or written) in one external transaction. This

is the case when the base register’s burst length bit (EBI_BRn[BL]) and port size bit (EBI_BRn[PS]) are

set such that one of two situations occur:

• Burst accesses are inhibited and the number of bytes requested by the master is greater than the

port size (16 or 32 bit) can accommodate in a single access.

• Burst accesses are enabled and the number of bytes requested by the master is greater than the

selected burst length (4 words or 8 words).

If this is the case, the EBI initiates multiple transactions until all the requested data is transferred. It should

be noted that all the transactions initiated to complete the data transfer are considered as an atomic

transaction, so the EBI does not allow other unrelated master accesses to intervene between the transfers.

In external master mode, this means that the EBI keeps BB asserted and does not grant the bus to another

master until the atomic transaction is complete.

Table 12-16 shows all the combinations of burst length, port size, and requested byte count that cause the

EBI to run multiple external transactions to fulfill the request.

In most cases, the timing for small accesses is the same as for normal single-beat and burst accesses, except

that multiple back-to-back external transfers are executed for each internal request. These transfers have

no additional dead cycles in-between that are not present for back-to-back stand-alone transfers except for

the case of writes with an internal request size greater than 64 bits, discussed in Section 12.4.2.6.2, “Small

Access Example #2: 32-byte Write with External TA.”

The following sections show a few examples of small accesses. The timing for the remaining cases in

Table 12-16 can be extrapolated from these and the other timing diagrams in this document.

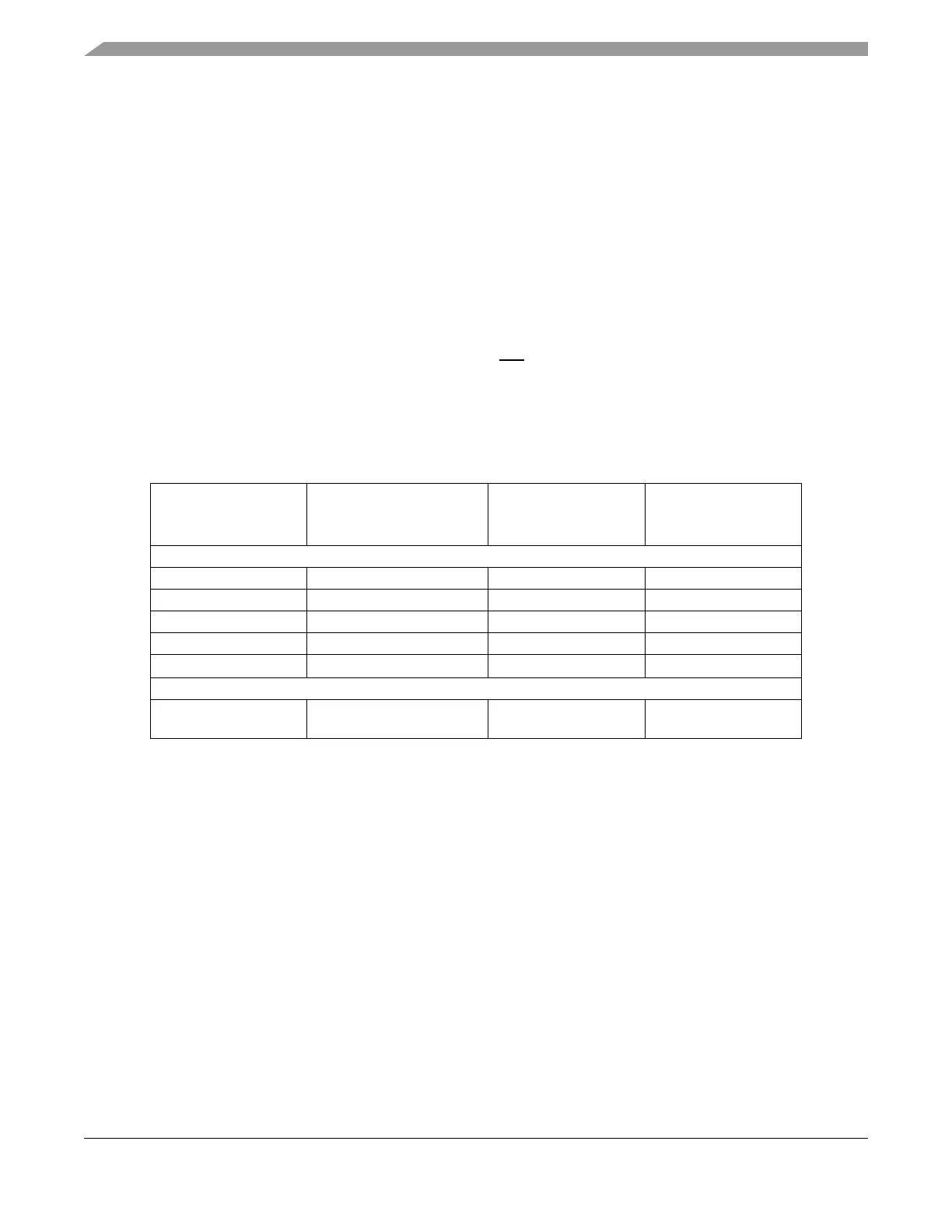

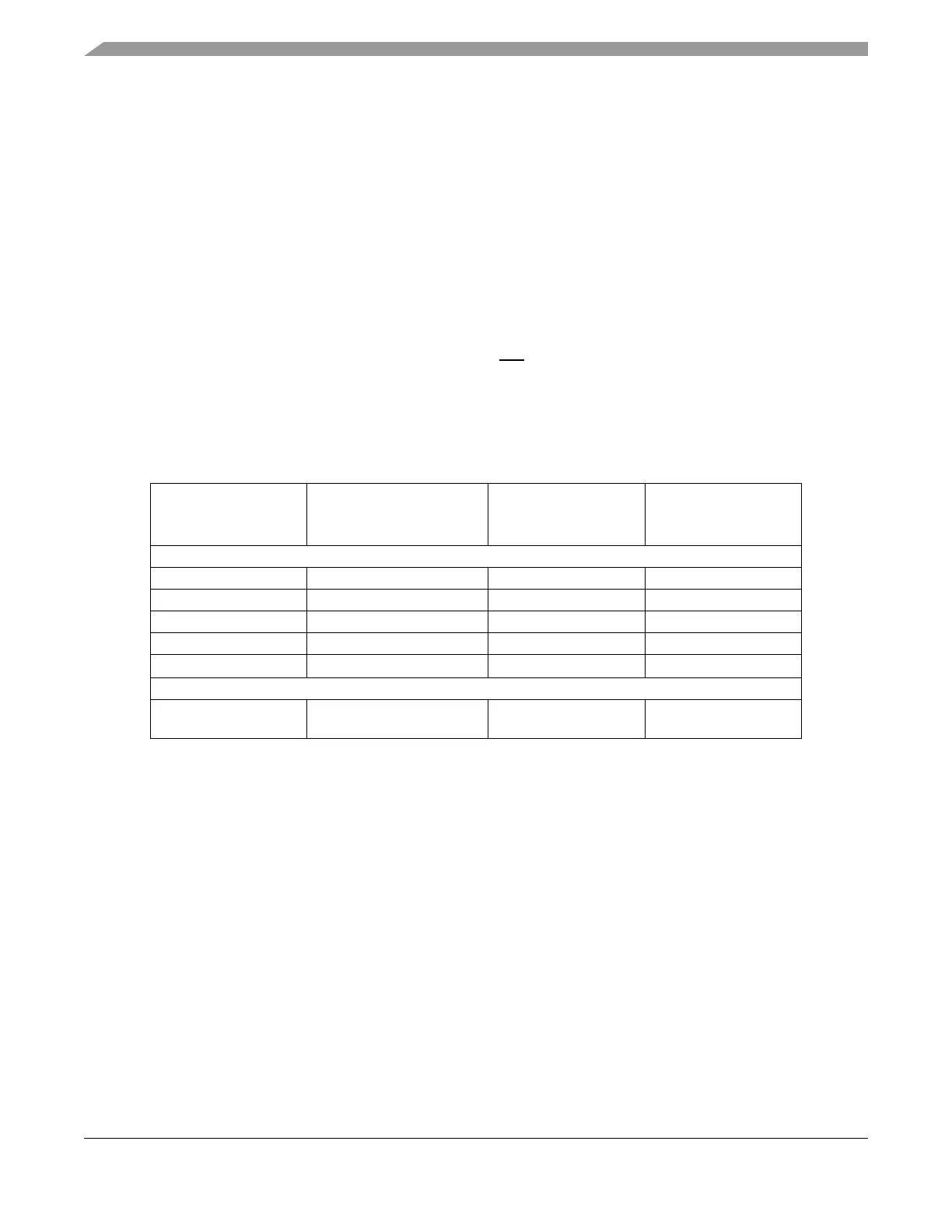

Table 12-16. Small Access Cases

Byte Count

Requested by Internal

Master

Burst Length Port Size

# External Accesses

to Fulfill Request

Non-Burstable Chip-Select Banks (BI=1) or Non-Chip-Select Access

4 1 beat 16-bit 2/1

1

1

In 32-bit data bus mode (DBM=0 in EBI_MCR), two accesses are performed. In 16-bit data bus mode

(DBM=1), one 2-beat burst access is performed and this is not considered a small access case. See

Section 12.4.2.11, “Non-Chip-Select Burst in 16-bit Data Bus Mode” for this special DBM=1 case.

8 1 beat 32-bit 2

8 1 beat 16-bit 4

32 1 beat 32-bit 8

32 1 beat 16-bit 16

Burstable Chip-Select Banks (BI=0)

32 4 words 16-bit (8 beats), 32-bit

(4 beats)

2

Loading...

Loading...