MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-39

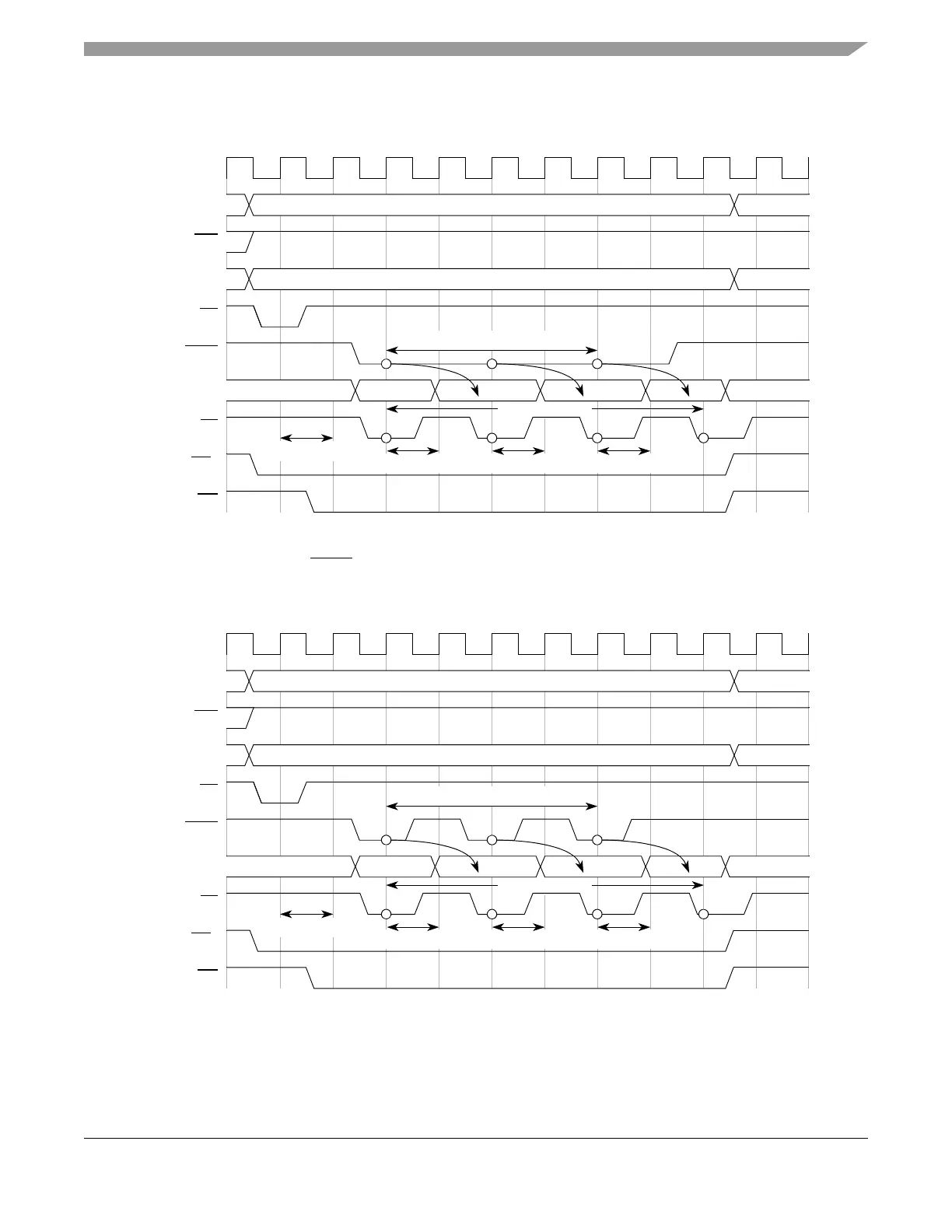

states between beats (BSCY). Figure 12-25 shows an example of the TBDIP = 0 timing for a 4-beat burst

with BSCY = 1.

Figure 12-25. Burst 32-bit Read Cycle, One Wait State between Beats, TBDIP = 0

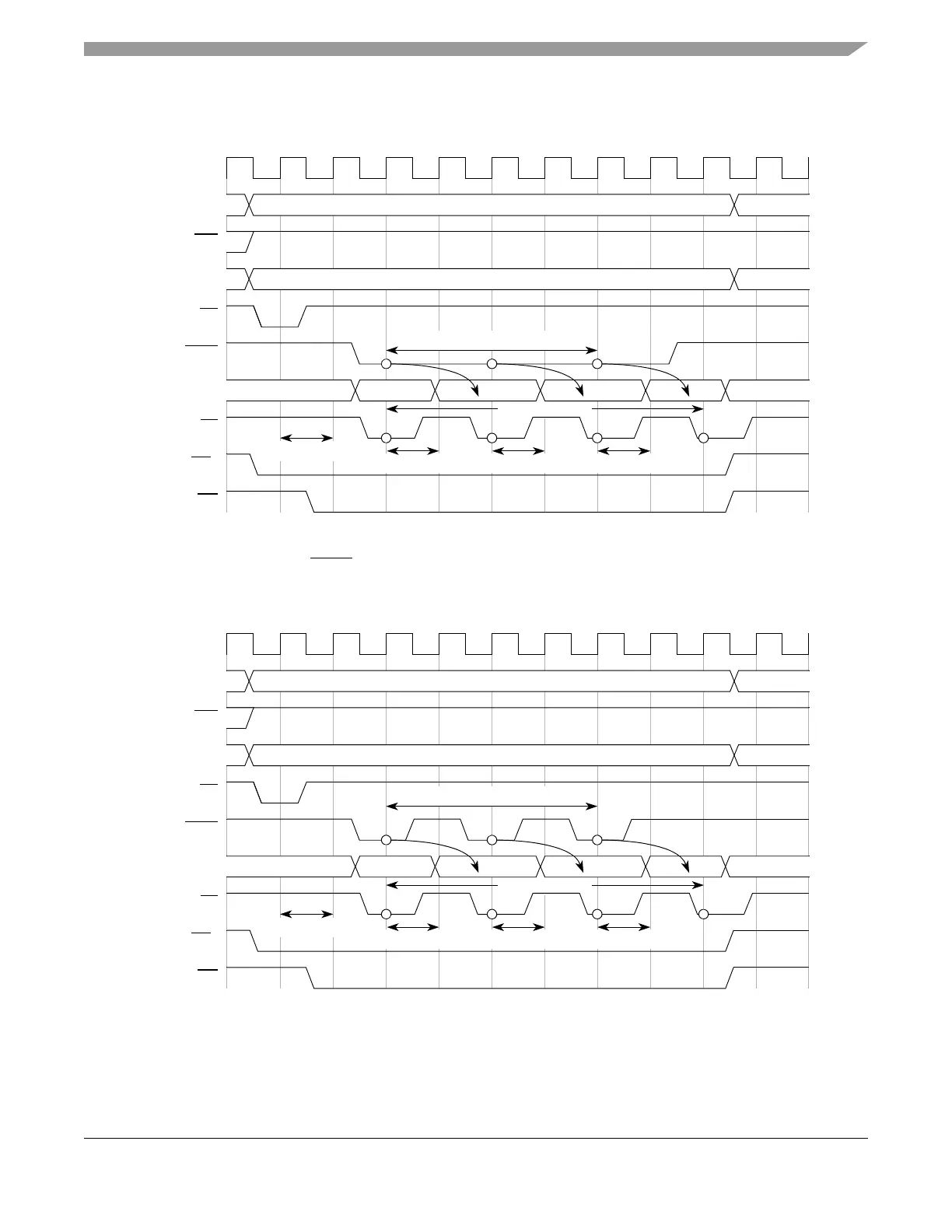

When using TBDIP = 1, the BDIP behavior changes to toggle between every beat when BSCY is a

non-zero value. Figure 12-26 shows an example of the TBDIP = 1 timing for the same four-beat burst

shown in Figure 12-25.

Figure 12-26. Burst 32-bit Read Cycle, One Wait State between Beats, TBDIP = 1

DATA is valid

Wait state

Wait state

CLKOUT

ADDR[8:31]

BDIP

DATA[0:31]

TA

RD_WR

TSIZ[0:1]

TS

OE

CSx

Expects more data

ADDR[29:31] = ‘000’

‘00’

Wait state Wait state

DATA is valid

Wait state

Wait state

CLKOUT

ADDR[8:31]

BDIP

DATA[0:31]

TA

RD_WR

TSIZ[0:1]

TS

OE

CSx

Expects more data

ADDR[29:31] = ‘000’

‘00’

Wait state Wait state

Loading...

Loading...