MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

12-50 Freescale Semiconductor

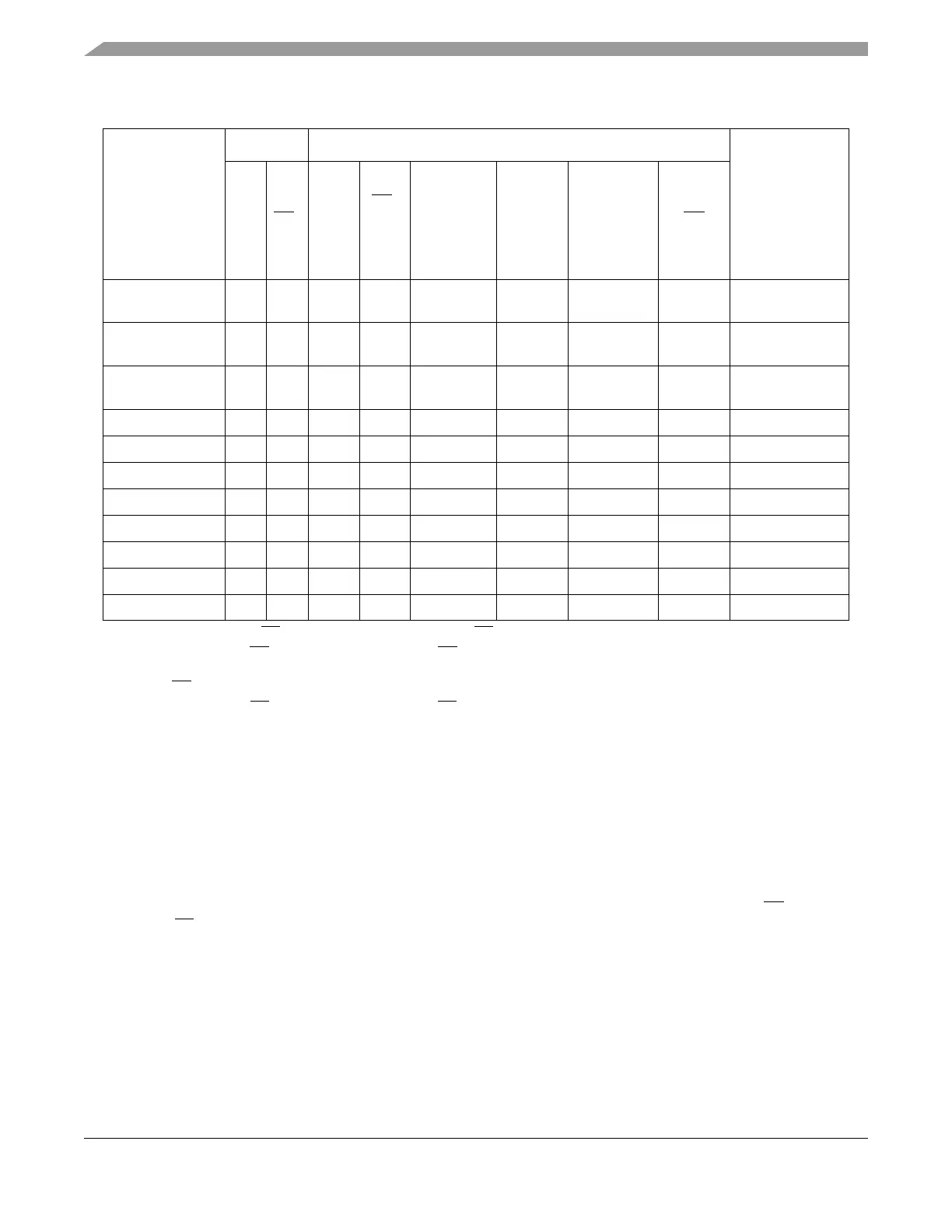

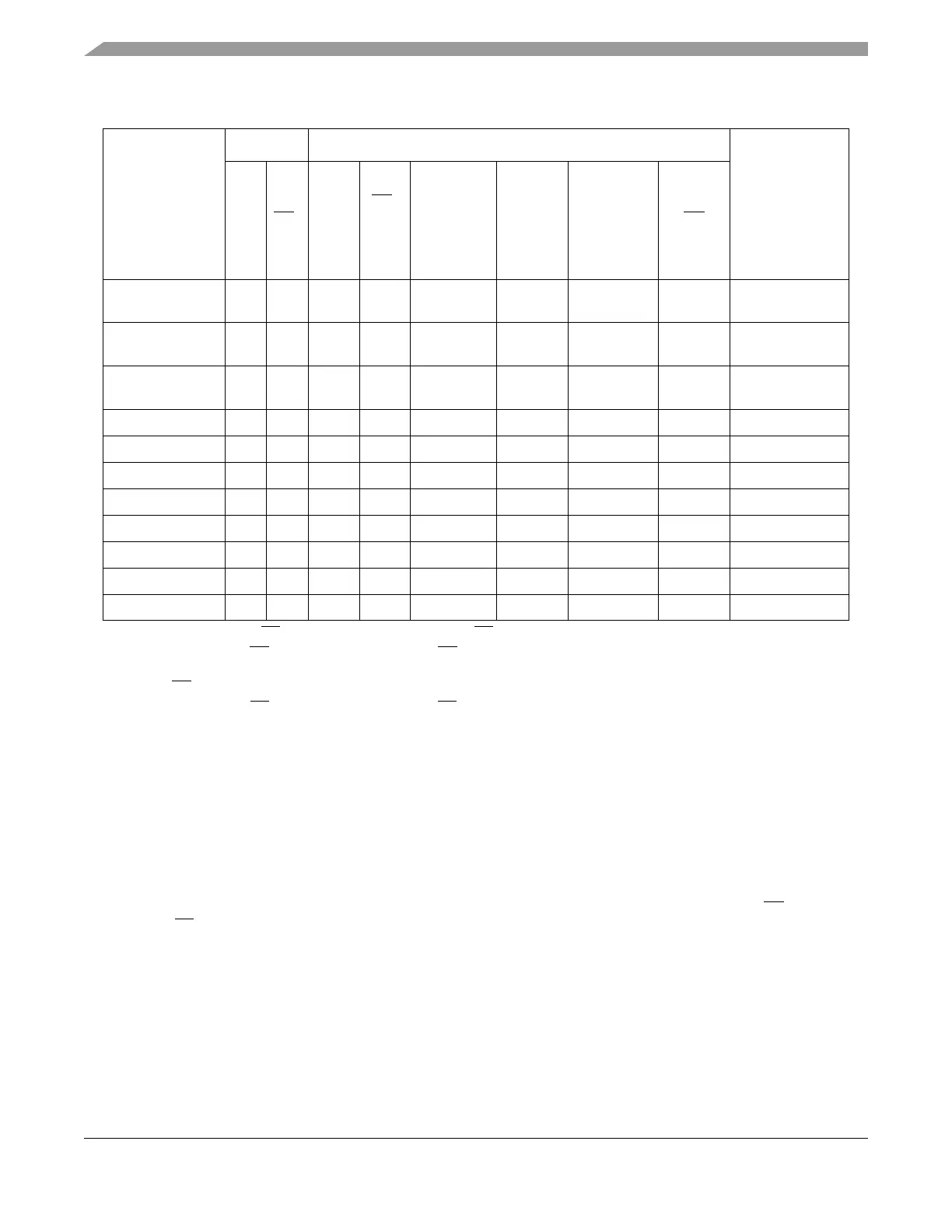

MCU Owner Busy 1 0/1

13

1X X X 1 X

8

MCU Owner

Busy

MCU Owner Busy 1 0/1 1 X 1 X X X MCU Owner

Busy

MCU Owner Busy 1 0/1 X X 1 0 X X MCU Owner

Busy

MCU Owner Busy 1 0/1 0 X X 1 1 X Ext. Bus Wait

MCU Owner Busy 1 0/1 0 X 0 X 1 X Ext. Bus Wait

MCU Owner Busy 1 0/1 0 X X 1 0 X Ext. Owner

MCU Owner Busy 1 0/1 0 X 0 X 0 X Ext. Owner

MCU Owner Busy 1 0/1 1 X 0 X 0 X MCU Owner Idle

Ext. Bus Wait 0 0/1

13

X

14

XX X 1 X

8

Ext. Bus Wait

Ext. Bus Wait 0 0/1 X X X X 0 X Ext. Owner

1

The Output column for BB shows the value EBI drives on BB for each state.

2

The Input column for BR shows the value driven on BR the previous cycle from an external source. The state machine

uses the previous clock value to avoid potential speed paths with trying to calculate bus grant based on a late-arriving

external BR

signal.

3

The Input column for BB shows the value driven on BB the previous cycle from an external source. The state machine

uses the previous clock value to ensure adequate switching time between masters driving the same signal and to avoid

potential speed paths.

4

This represents an internal EBI signal that indicates whether an internal request for use of the external bus is pending.

After a transaction for a pending request has been started on the external bus, this internal signal is cleared. The state

machine uses the previous clock value to avoid potential speed paths with trying to calculate bus grant based on a

late-arriving internal request signal.

5

This represents an internal EBI signal that indicates whether the internal MCU (0) or external master (1) currently has

higher priority.

6

This represents an internal EBI signal that indicates whether an EBI-mastered transaction on the bus is in progress this

cycle or is going to start the next cycle (and thus has already been committed internally).

7

This represents an internal EBI signal that indicates whether the bus was granted to an external master (BG =0,

previous BB

= 1) during the previous 3 cycles.

8

RGB is always low in this state, thus it is ignored in the transition logic.

9

RGB is always low in this state, thus it is ignored in the transition logic.

10

The ETP signal is never asserted in states where it is shown as an ‘X’ for all transitions.

11

RGB is always high in this state, thus it is ignored in the transition logic.

Table 12-22. Internal Arbiter Truth Table (Continued)

State

Outputs Inputs

Next State

BG BB

1

BR

2

(previ

ous)

BB

3

(previ

ous)

MCU

Internal

Request

Pending

(IRP)

4

(previous)

External

has

Higher

Priority

(EHP)

5

MCU Ext.

Transaction

in Progress

(or starting

next cycle)

(ETP)

6

Recent

BG

(RBG)

7

Loading...

Loading...