MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-55

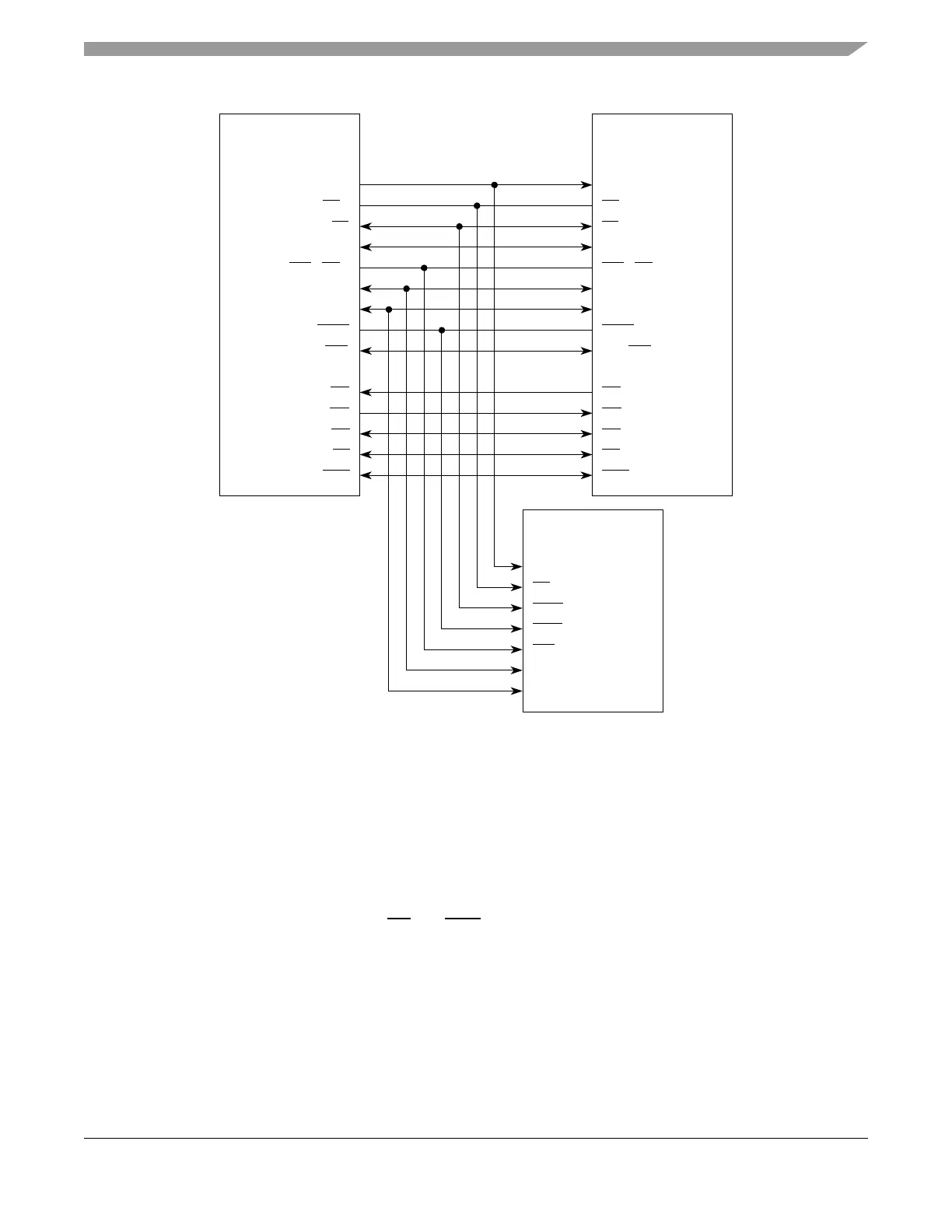

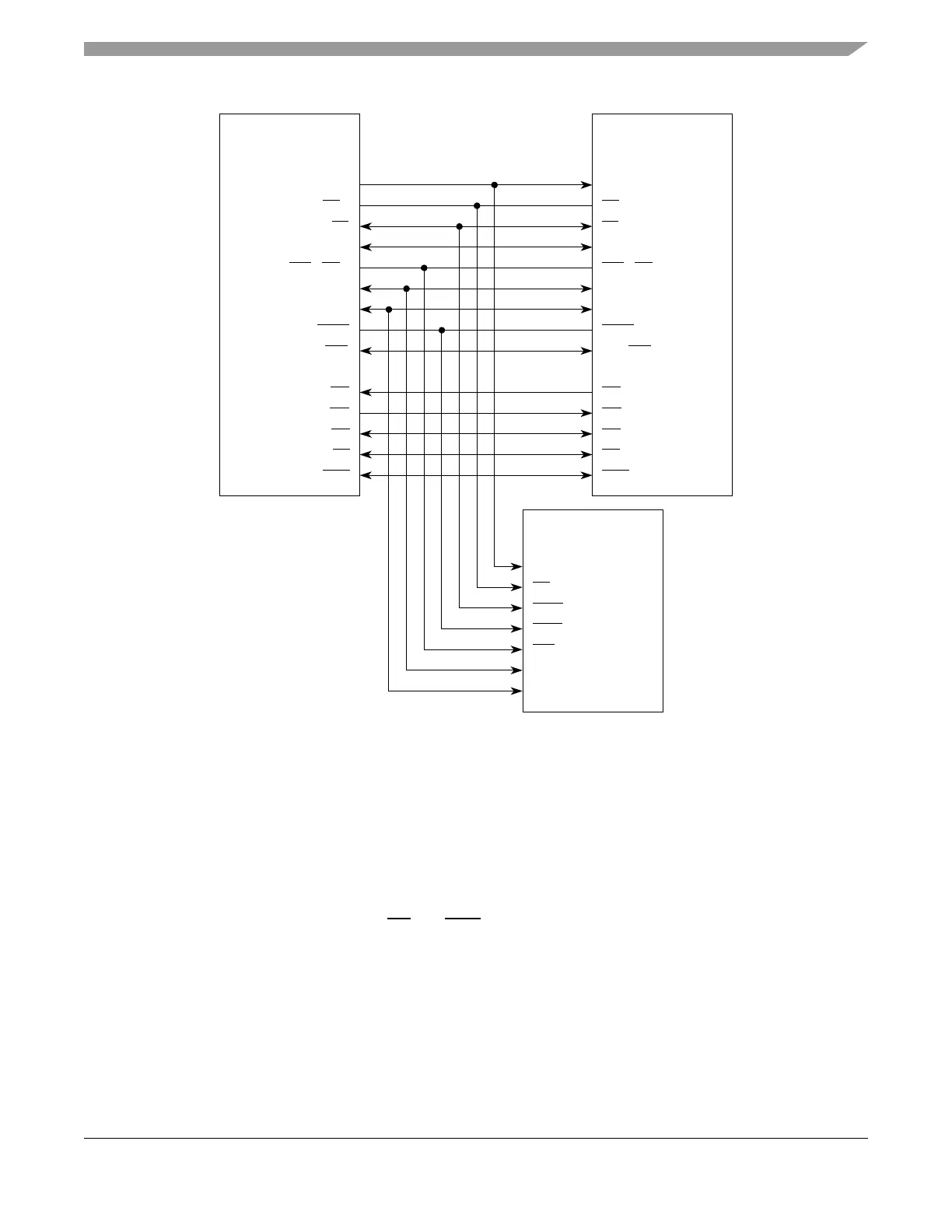

Figure 12-38. MCU Connected to External Master and SDR Memory

When the external master requires external bus accesses, it takes ownership on the external bus, and the

direction of most of the bus signals is inverted, relative to its direction when the MCU owns the bus.

To operate two masters in external master mode, one must be configured for internal arbitration and the

other must be configured for external arbitration. Connecting three or more masters together in the same

system is not supported by this EBI.

Most of the bidirectional signals shown in Figure 12-38 are only driven by the EBI when the EBI owns the

external bus. The only exceptions are the TA and TEA signals (described in Section 12.4.2.9, “Termination

Signals Protocol”) and the DATA bus, which are driven by the EBI for external master reads to internal

address space. As long as the external master device follows the same protocol for driving signals as this

EBI, there is no need to use the open drain mode of the pads configuration module for any EBI pins.

The Power Architecture storage reservation protocol is not supported by the EBI. Coherency between

multiple masters must be maintained via software techniques, such as event passing.

CLKOUT

CS

0

TS

TSIZ[0:1]

WE0/BE0

ADDR[8:31]*

DATA[0:31]

BDIP

RD_WR

BR

BG

BB

TA

TEA

CK

CS

ADV

BAA

WE

A[0:21]

DATA[0:31]

SDR

Memory

MCU

(Configured for

Internal Arbitration)

EXTAL

CS

0

TS

TSIZ[0:1]

WE0/BE0

ADDR[8:31]*

DATA[0:31]

BDIP

RD_WR

BR

BG

BB

TA

TEA

MCU

(Configured for

External Arbitration)

* Only ADDR[8:29] are connected to the 32-bit SDR memory.

Loading...

Loading...