MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-59

latency of an external to internal cycle varies depending on which internal module is being accessed and

how much internal bus traffic is going on at the time of the access.

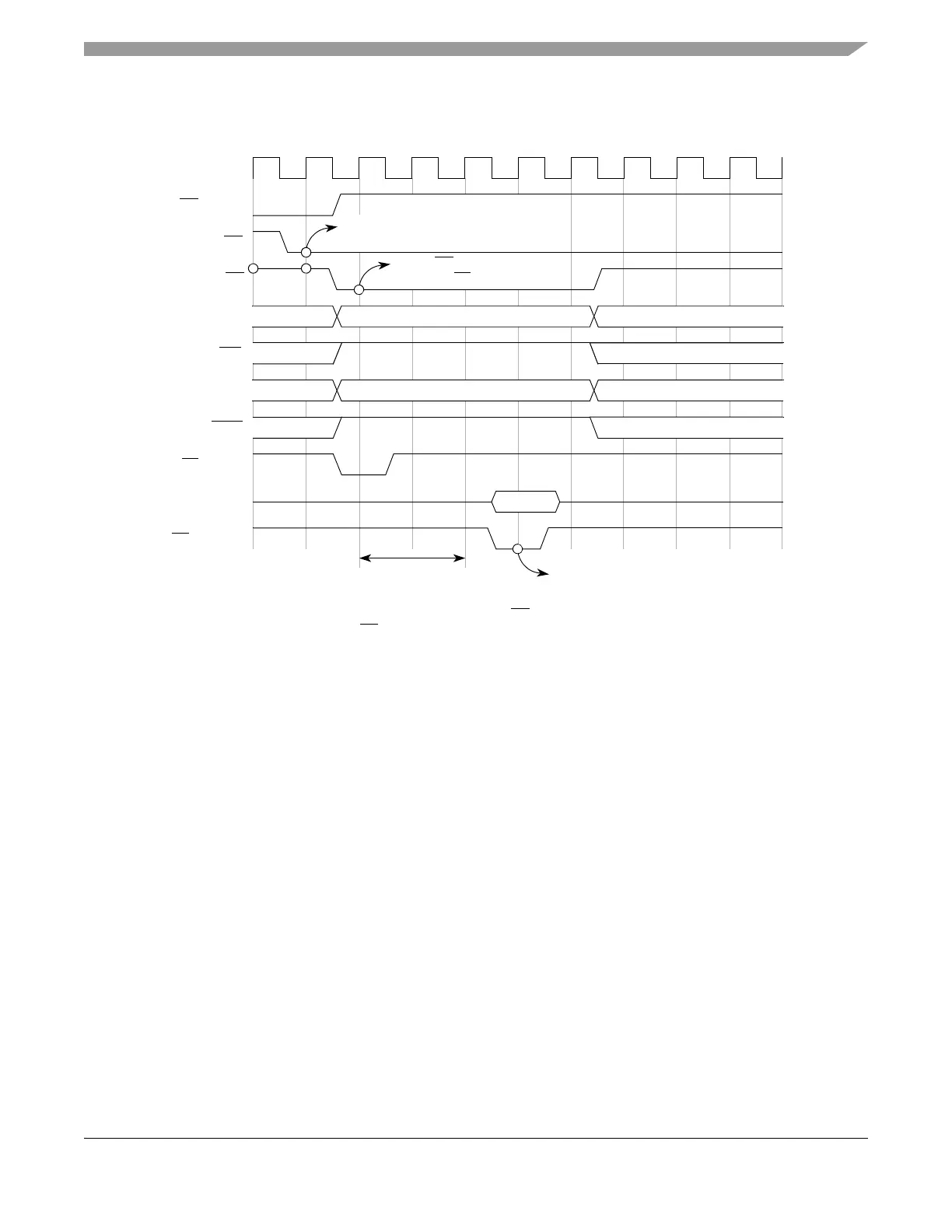

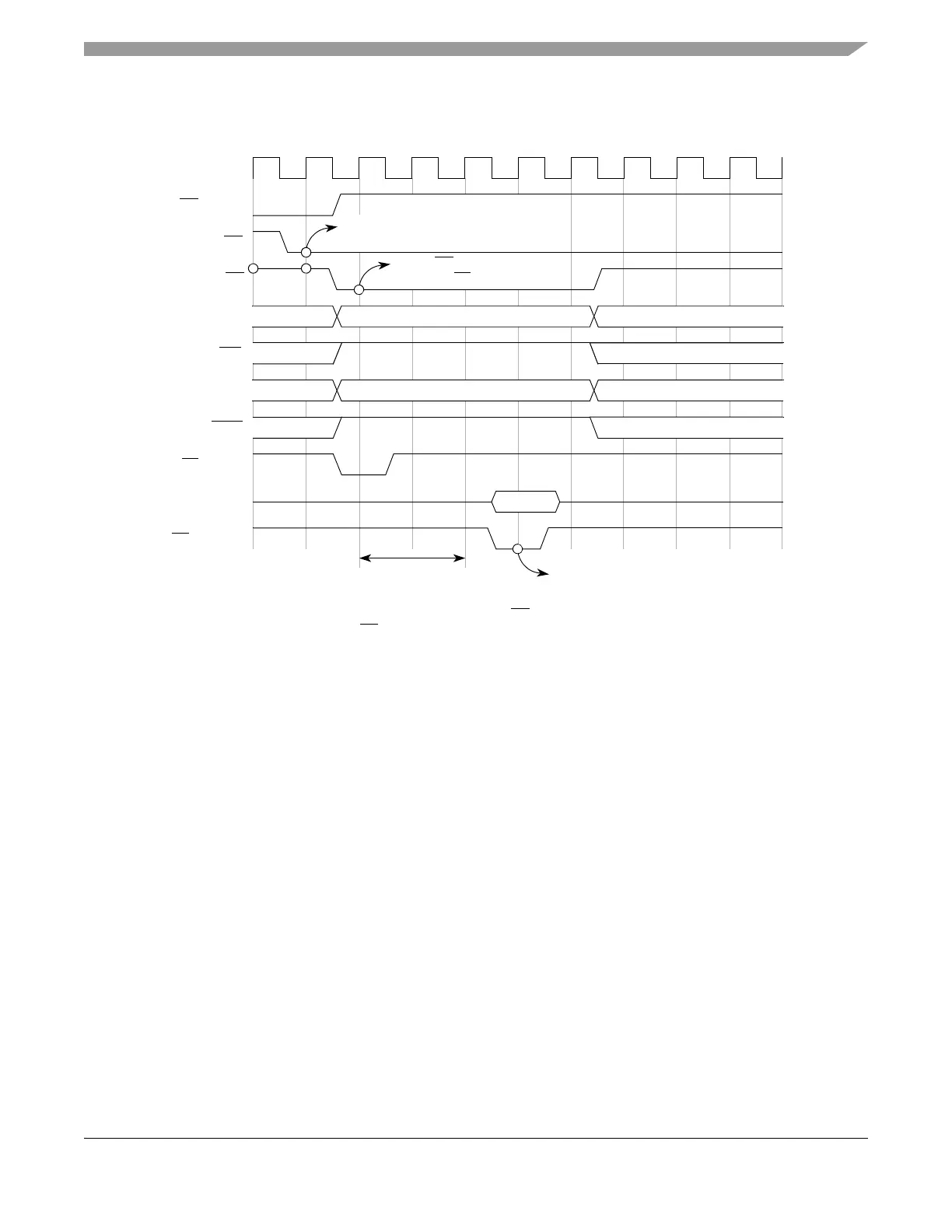

Figure 12-41. External Master Read from MCU

Receive bus grant and bus busy

negated for 2nd cycle

Assert BB drive address

and assert TS

Using the internal arbiter

CLKOUT

BR

(Input)

RD_WR

TSIZ[0:1]

BDIP

BG

BB

ADDR[8:31]

DATA[0:31]

TS

(Input)

Minimum

2 wait states

If the external master is another MCU with this EBI, then BB and other control pins are turned off

*

*

as shown due to use of latched TA internally. This extra cycle is not required by the slave EBI.

DATA is valid

TA

(Output)

Loading...

Loading...