MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

12-58 Freescale Semiconductor

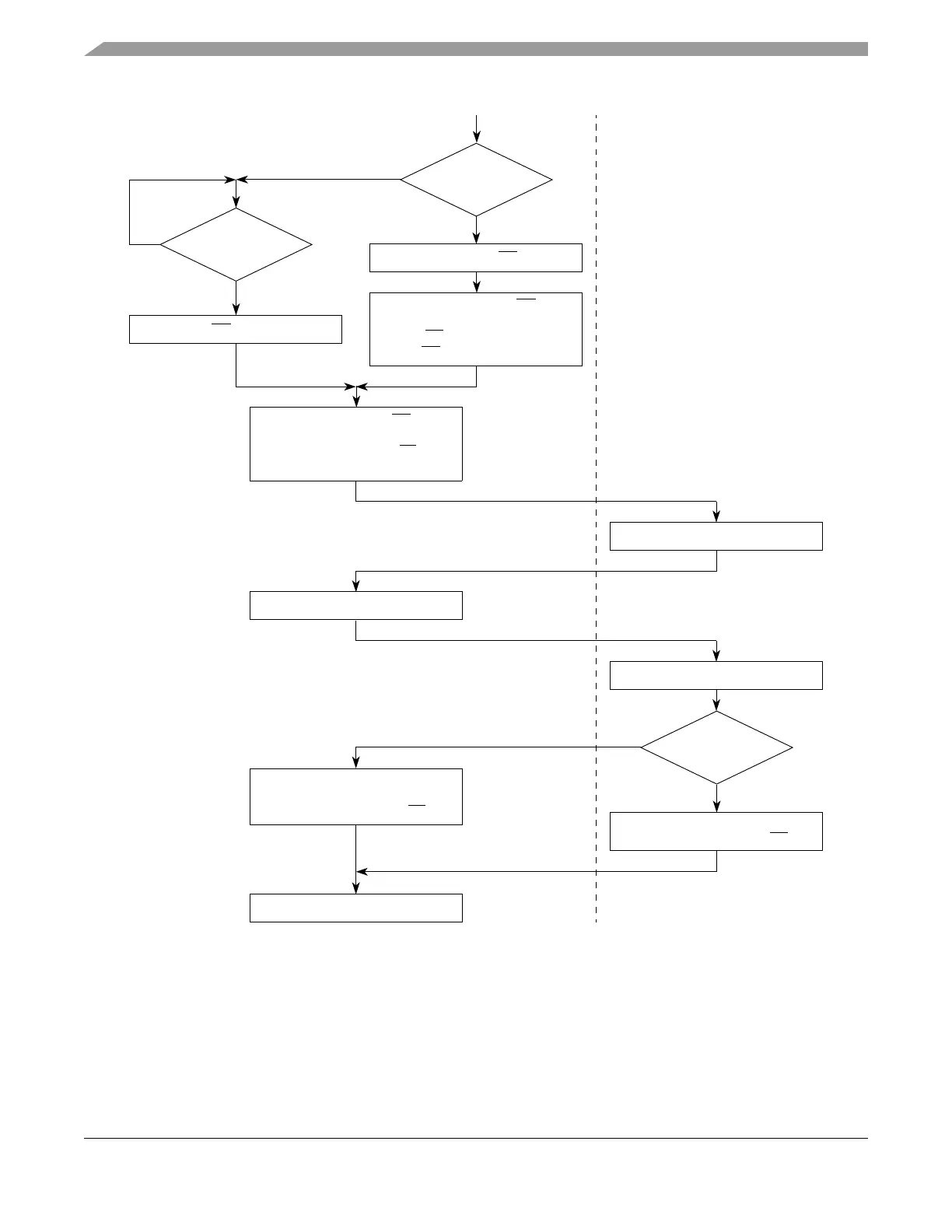

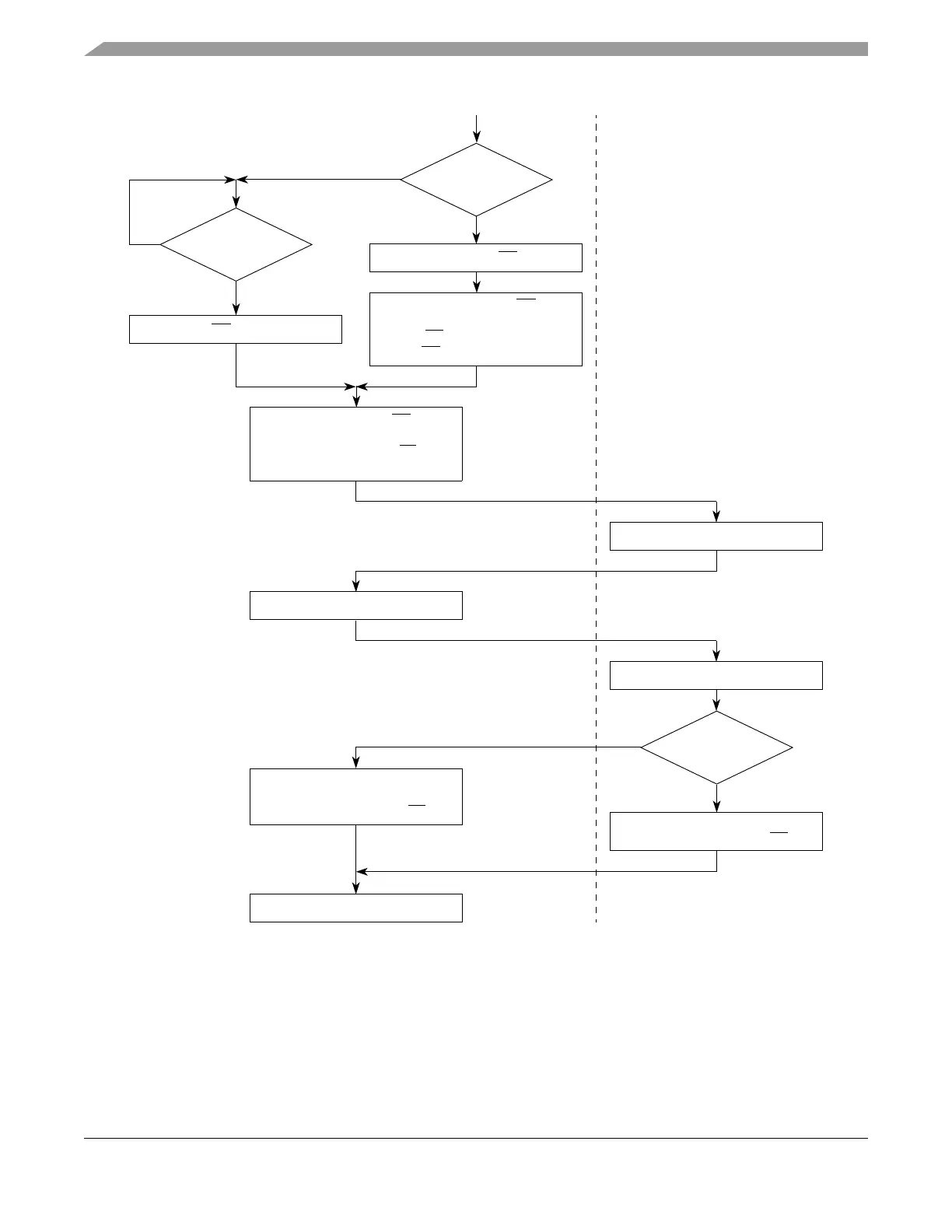

Figure 12-40. Basic Flow Diagram of an External Master Write Cycle

Figure 12-41 and Figure 12-42 describe read and write cycles from an external master accessing internal

space in the MCU. Note that the minimal latency for an external master access is 3 clock cycles. The actual

External Master EBI (Slave)

No

Yes

External

Arbitration*

?

Request Bus (BR)

Receives Bus Grant (BG)

Asserted from External Arbiter**

Receives BB

Negated for 2 Cycles

Negates BR

if No Other Requests

No

Yes

External

Master has

Priority***

Negates BG if Asserted

Asserts Bus Busy (BB)

if No Other Master is Driving

Assert Transfer Start (TS)

Drives Address and Attributes

?

Receives Address

No

Yes

Address

in Internal Memory

Map

?

Other Shared Device

Asserts

Transfer Acknowledge (TA

)

Receives Data

Drives Data

Receives Data

Asserts

Transfer Acknowledge (TA

)

This refers to whether the external master device is configured for external or internal arbitration.

*

External arbiter is the EBI unless a central arbiter device is used.

**

Determined by the internal arbiter of the external master device.

***

Loading...

Loading...