MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 13-13

NOTE

In the event that blocks are not present (due to configuration or total

memory size), the LOCK bits will default to locked, and will not be

writable. The reset value will always be 1 (independent of the shadow

block), and register writes will have no effect.

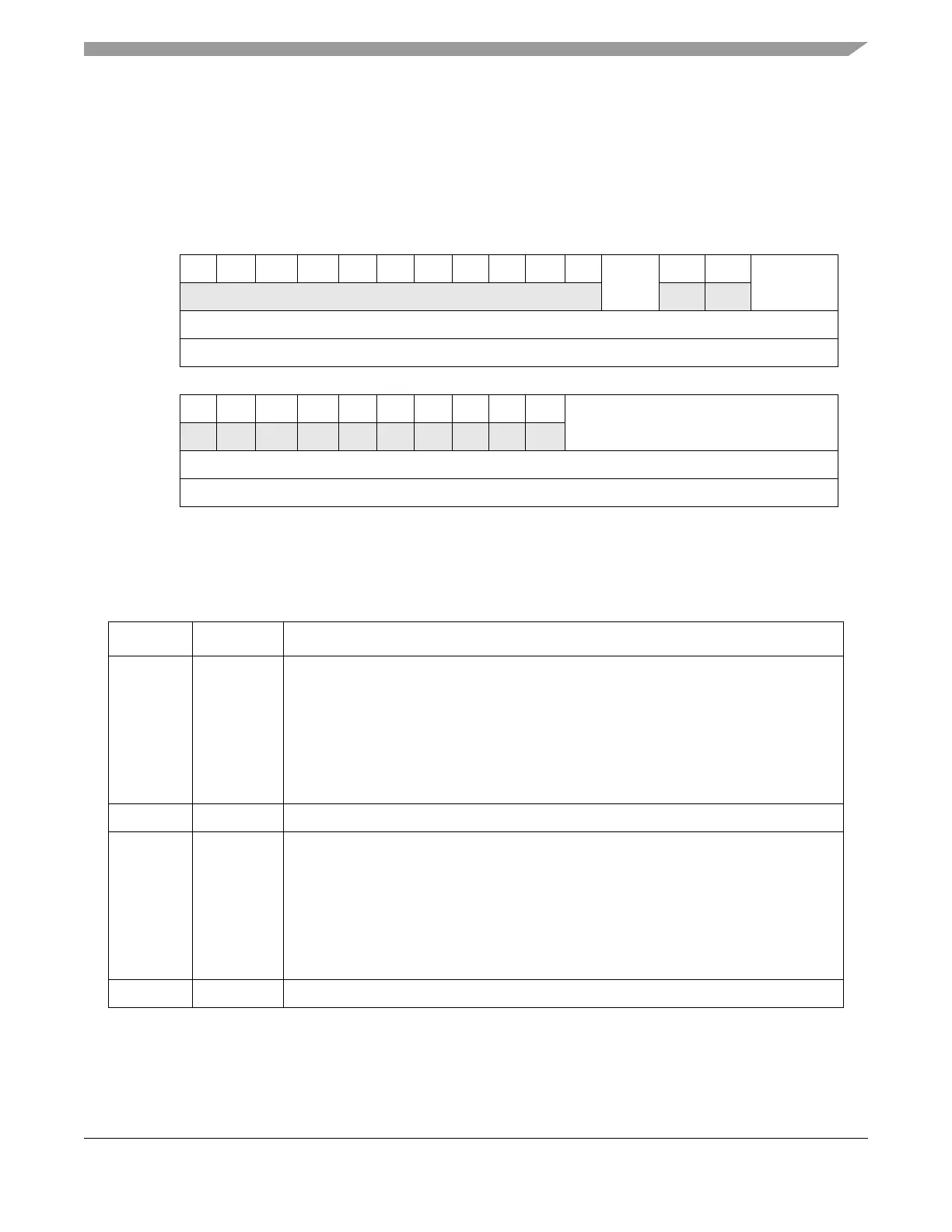

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

RLME 0 0 0 0 0 0 0 0 0 0 SLOCK 1 1 MLOCK

W

Reset 0 0 0 0 0 0 0 0 0 0 0 1

1

1

1

1

1

1

1

1

1

Reg Addr Base (0xC3F8_8000) + 0x0004

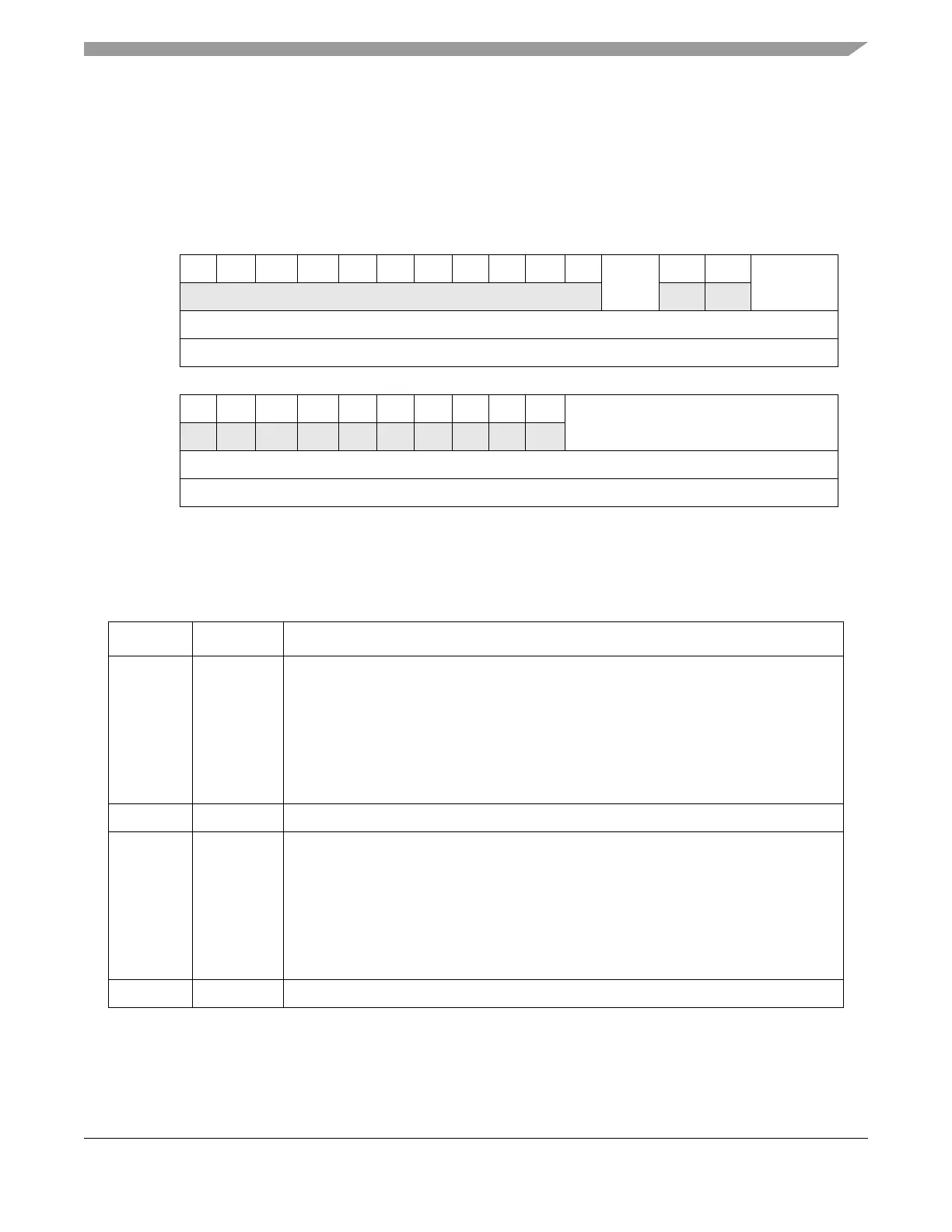

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R1 1 1 1 1 1 1 1 1 1 LLOCK

W

Reset 1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Reg Addr Base (0xC3F8_8000) + 0x0004

1

The reset value of these bits is determined by flash values in the shadow row. An erased array will cause

the reset value to be 1

Figure 13-6. Low-/Mid-Address Space Block Locking Register (FLASH_LMLR)

Table 13-8. FLASH_LMLR Field Descriptions

Bits Name Description

0 LME Low- and mid-address lock enable. Enables the locking register fields (SLOCK, MLOCK

and LLOCK) to be set or cleared by register writes. This bit is a status bit only, and may not

be written or cleared, and the reset value is 0. The method to set this bit is to write a

password, and if the password matches, the LME bit will be set to reflect the status of

enabled, and is enabled until a reset operation occurs. For LME, the password

0xA1A1_1111 must be written to the FLASH_LMLR.

0 Low- and mid-address locks are disabled, and cannot be modified.

1 Low- and mid-address locks are enabled and can be written.

1–10 — Reserved.

11 SLOCK Shadow lock. Locks the shadow row from programs and erases. The SLOCK bit is not

writable if a high voltage operation is suspended.

Upon reset, information from the shadow row is loaded into the SLOCK bit. The SLOCK bit

may be written as a register. Reset will cause the bits to go back to their shadow row value.

The default value of the SLOCK bit (assuming the corresponding shadow row bit is erased)

would be locked. SLOCK is not writable unless LME is high.

0 Shadow row is available to receive program and erase pulses.

1 Shadow row is locked for program and erase.

12–13 — Reserved.

Loading...

Loading...