MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

14-22 Freescale Semiconductor

14.3.4.2.10 Transmit Control Register (TCR)

The TCR is read/write and is written by the user to configure the transmit block. This register is cleared at

system reset. Bits 29 and 30 should be modified only when ECR[ETHER_EN] = 0.

30 DRT Disable receive on transmit.

0 Receive path operates independently of transmit (use for full-duplex or to

monitor transmit activity in half-duplex mode).

1 Disable reception of frames while transmitting (normally used for

half-duplex mode).

31 LOOP Internal loopback. If set, transmitted frames are looped back internal to the

device and the transmit output signals are not asserted. The system clock is

substituted for the FEC_CLK when LOOP is asserted. DRT must be set to

zero when asserting LOOP.

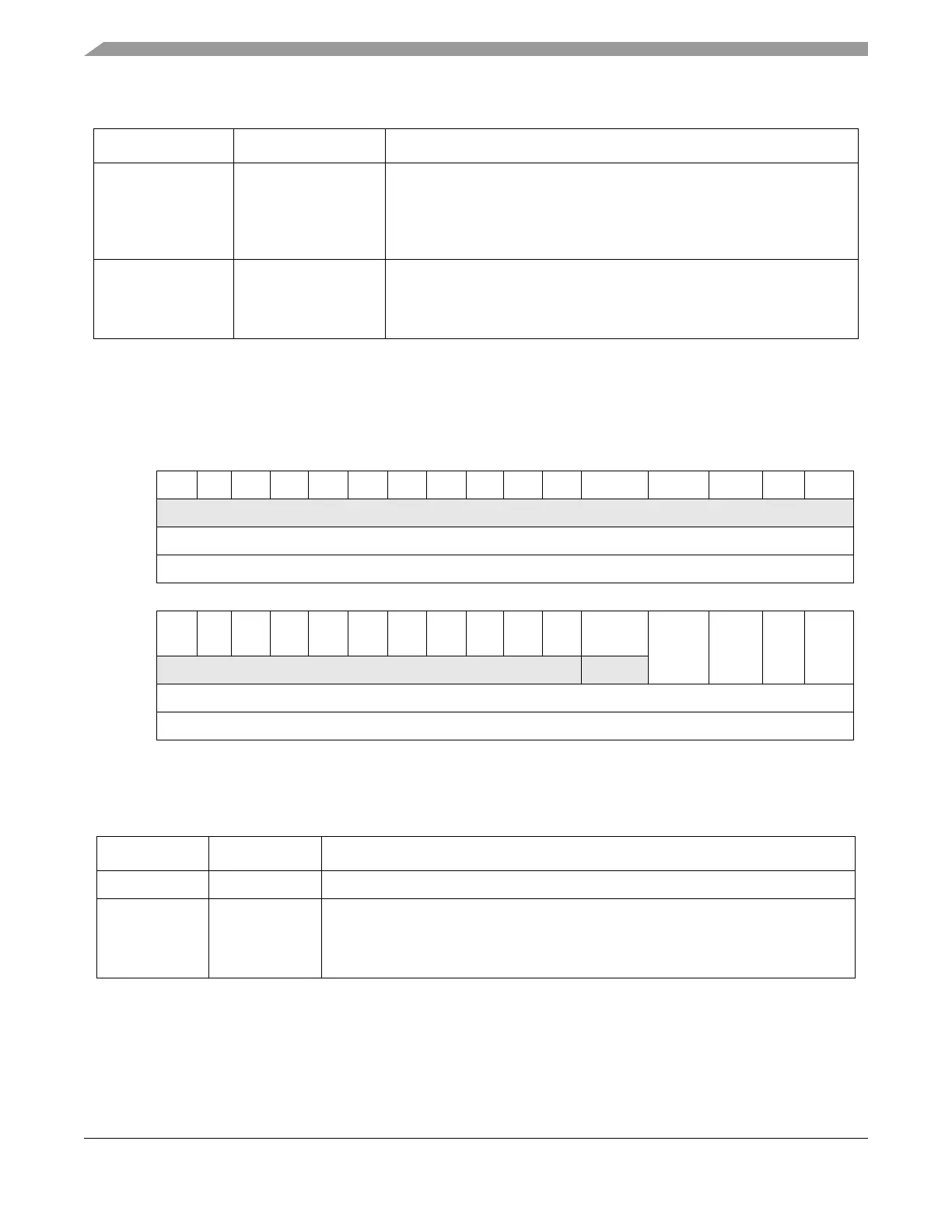

0 12345678910 11 12 13 1415

R00000000000 0 0 0 0 0

W

Reset00000000000 0 0 0 0 0

Address Base + 0x00C4

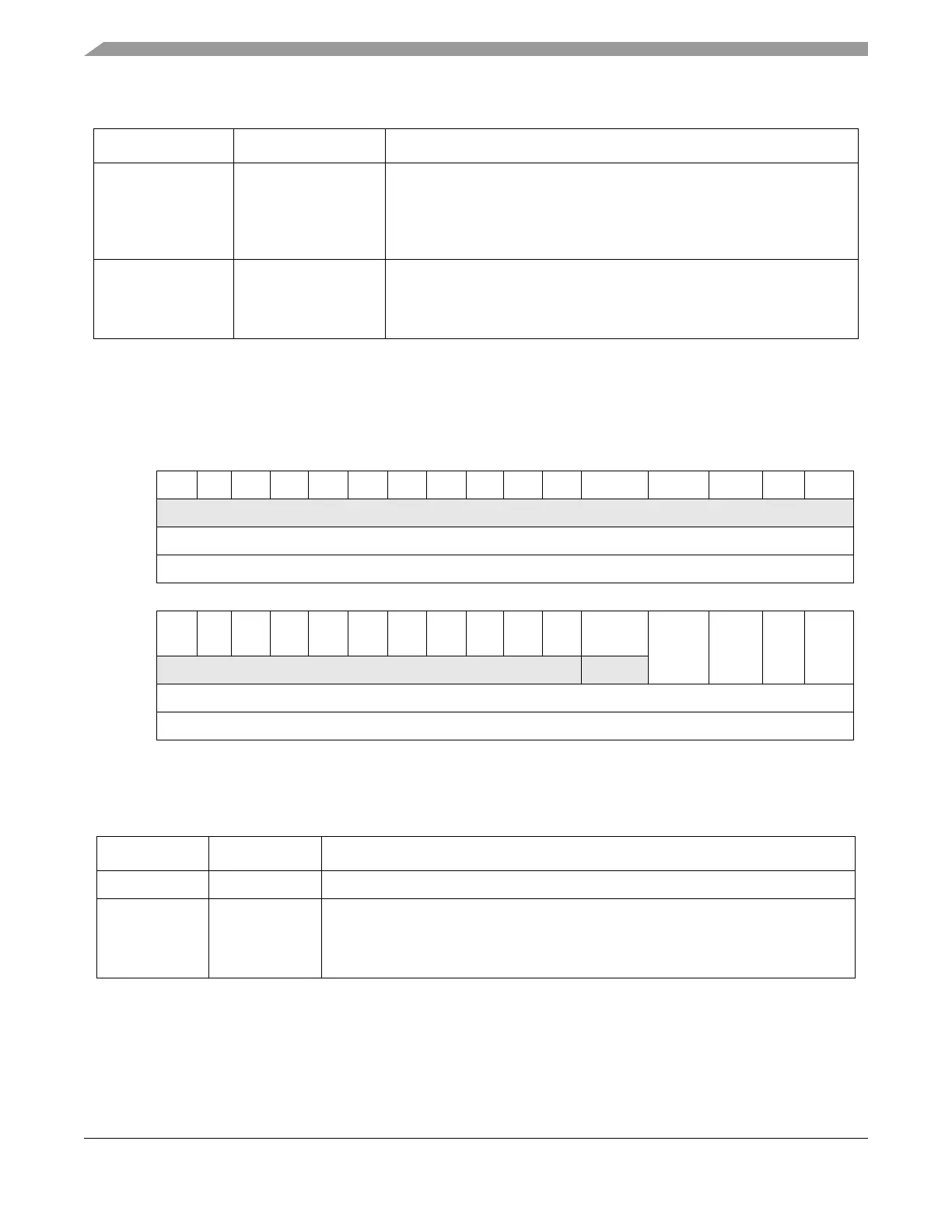

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000000000RFC_

PAUSE

TFC_

PAUS E

FDEN HBC GTS

W

Reset00000000000 0 0 0 0 0

Address Base + 0x00C4

Figure 14-12. Transmit Control Register (TCR)

Table 14-15. TCR Field Descriptions

Bits Name Description

0–26 — Reserved, should be cleared.

27 RFC_PAUSE Receive frame control pause. This read-only status bit will be asserted when a

full-duplex flow control pause frame has been received and the transmitter is paused

for the duration defined in this pause frame. This bit will automatically clear when the

pause duration is complete.

Table 14-14. RCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...