MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-53

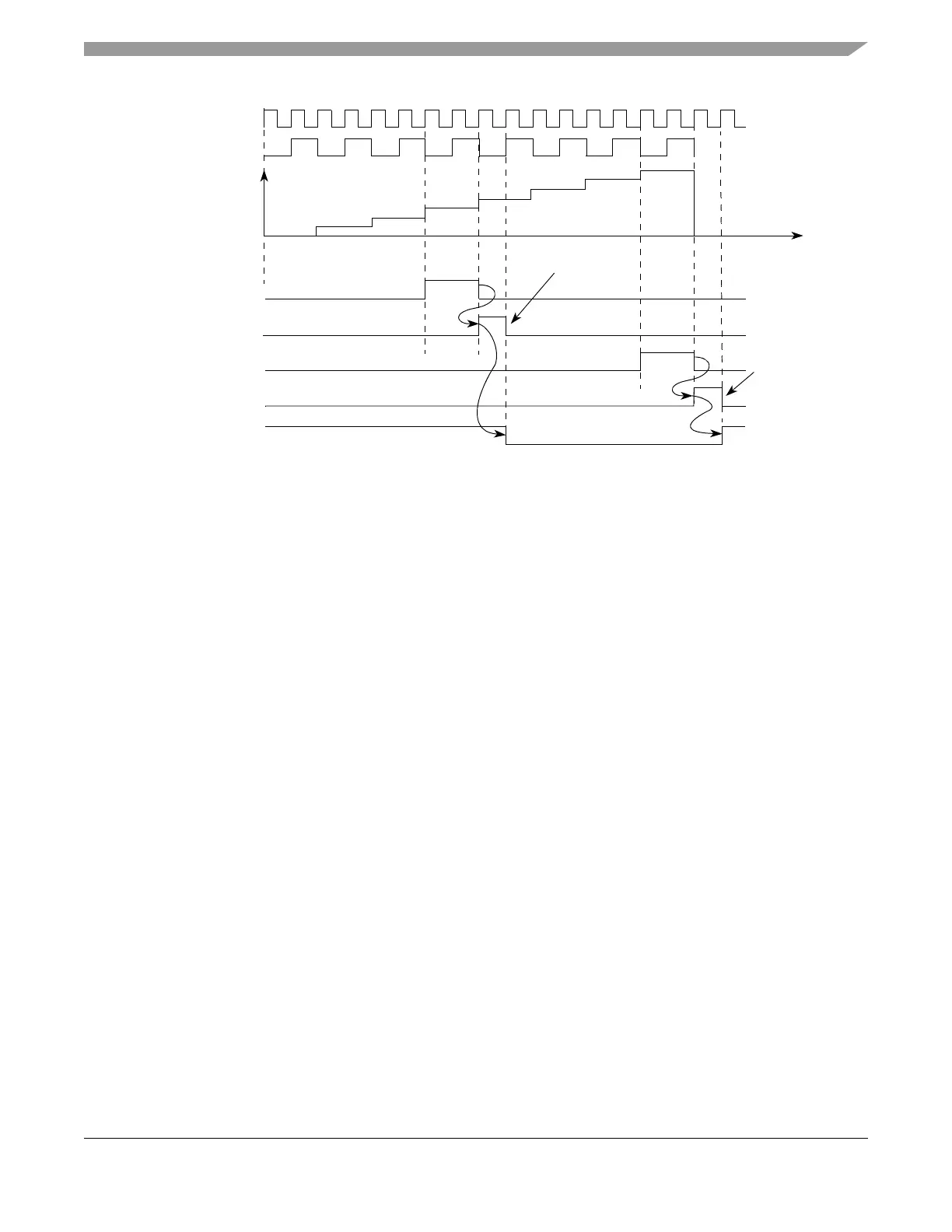

Figure 17-41. eMIOS OPWFMB Mode Example — A1/B1 Match to Output Register Delay

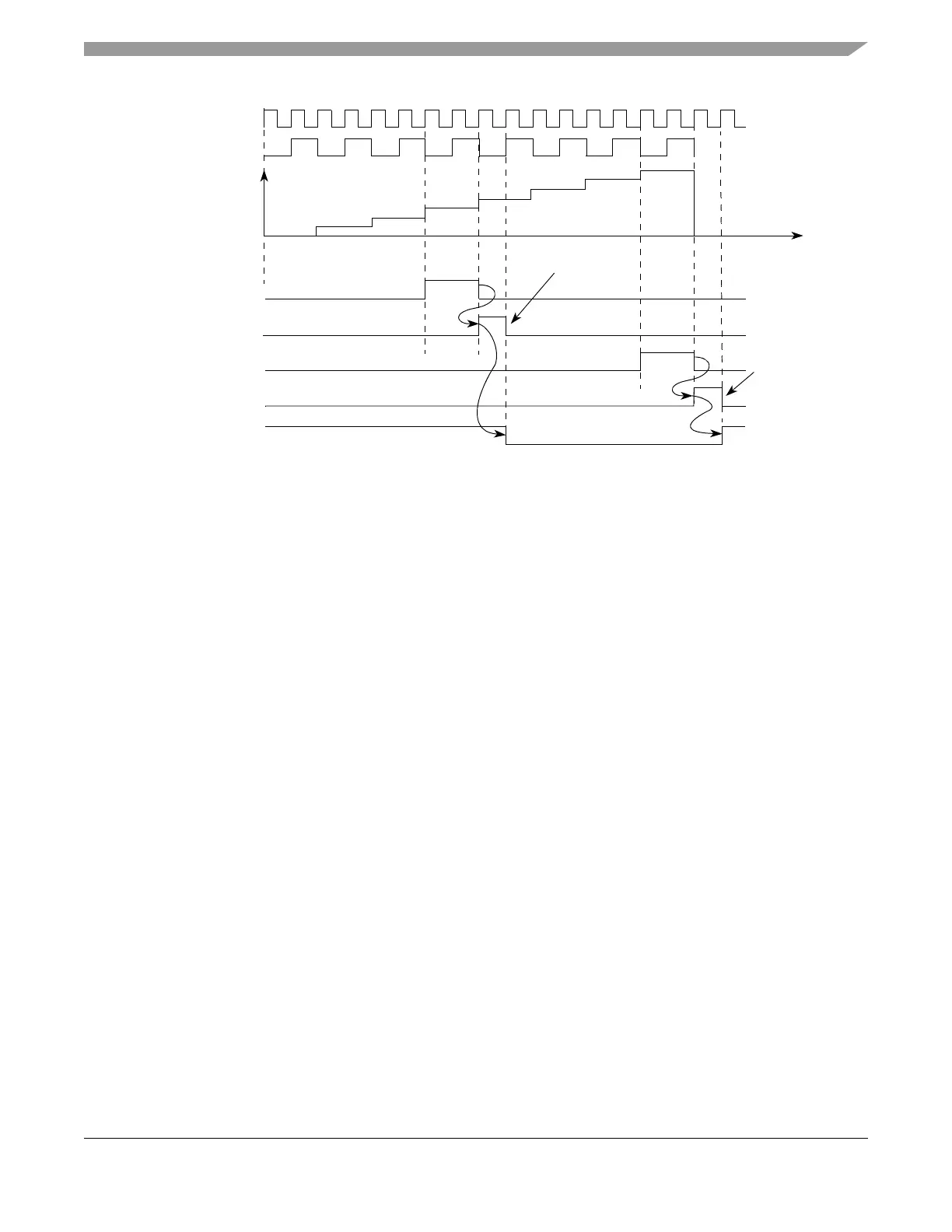

Figure 17-42 shows the generated output signal if A1 is 0. Because the counter does not reach zero in this

mode, the channel internal logic infers a match as if A1 = 1, with the difference that in this case the positive

edge of the match signal is used to trigger the output flip-flop transition instead of the positive edge that is

used when A1 = 1. Note that the A1 positive edge match signal from cycle (n+1) occurs at the same time

as the B1 match negative edge from cycle (n). This allows the use of the A1 match positive edge to mask

the B1 match negative edge when they occur at the same time. The result is that no transition occurs on

the output flip-flop, and a 0% duty cycle is generated.

8

1

4

A1 Match

5

A1 Value 0x000004

A1 Match

A1 Match Negative

Output Flip-Flop

Time

B1 Match

B1 Match

B1 Match Negative

B1 Value 0x000008

System Clock

Prescaled Clock

Edge Detection

Edge Detection

Negative

Edge Detect

Negative

Edge Detect

EDPOL = 0

EMIOS_CCNTR

Loading...

Loading...