MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-22 Freescale Semiconductor

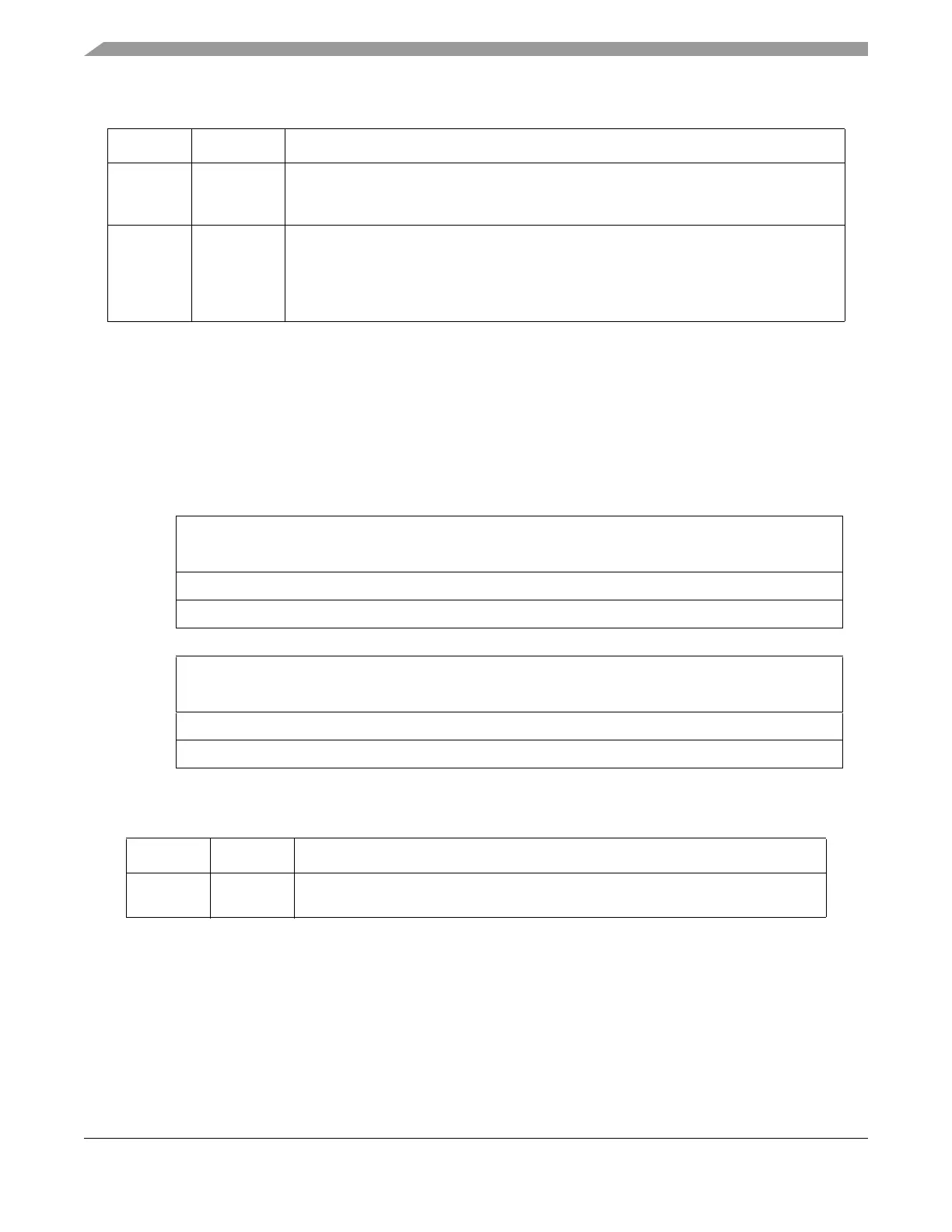

18.4.2.1.3 eTPU MISC Compare Register (ETPU_MISCCMPR)

The multiple input signature calculator compare register (ETPU_MISCCMPR) holds the 32-bit signature

expected from the whole shared code memory (SCM) array. This register must be written by the host with

the 32-bit word to be compared against the calculated signature at the end of the MISC cycle. This register

is global to both eTPU engines. For more details, refer to the eTPU reference manual.

18.4.2.1.4 eTPU SCM Off-Range Data Register (ETPU_SCMOFFDATAR)

ETPU_SCMOFFDATAR holds the 32-bit value returned when the SCM array is accessed at non

implemented addresses, either by the host or by the microengine. This register can be written by the host

with the 32-bit instruction to be executed by the microengine to recover from runaway code. This register

is global to both ETPU engines.

24 WR Read/Write selection. This bit selects the direction of the coherent data transfer.

0 Read operation. Data transfer is from the selected parameter RAM address to the PB.

1 Write operation. Data transfer is from the PB to the selected parameter RAM address.

25 – 31 PARM1

[0:6]

Channel parameter number 1. This field in concatenation with CTBASE[3:0] determines

the address offset (from the SDM base) of the parameter which is the destination or source

(defined by WR) of the coherent transfer. The SDM address offset of the parameter is

{CTBASE, PARM1}*4.Note that PARM1 allows non-contiguous parameters to be

transferred coherently

1

.

1

The parameter pointed by {CTBASE, PARM0} is the first transferred.

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R EMISCCMP

W

Reset0000000000000000

Reg Addr Base + 0x0_000C

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R EMISCCMP

W

Reset0000000000000000

Reg Addr Base + 0x0_000C

Figure 18-7. eTPU MISC Compare Register (ETPU_MISCCMPR)

Table 18-9. ETPU_MISCCMPR Field Descriptions

Bits Name Description

0 – 31 EMISCCM

P[0:31]

Expected multiple input signature calculator compare register value. For more

information, refer to the eTPU reference manual.

Table 18-8. ETPU_CDCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...