MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-25

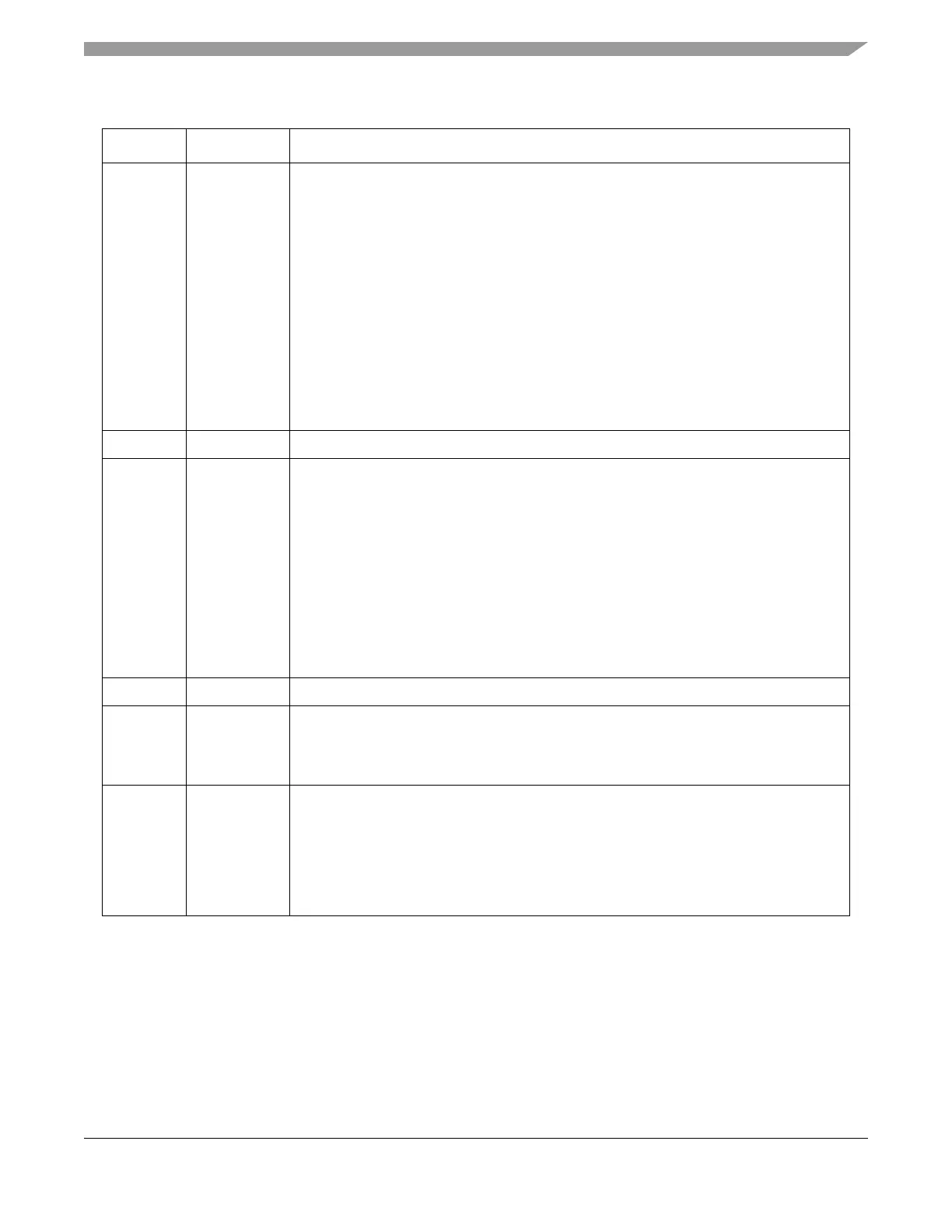

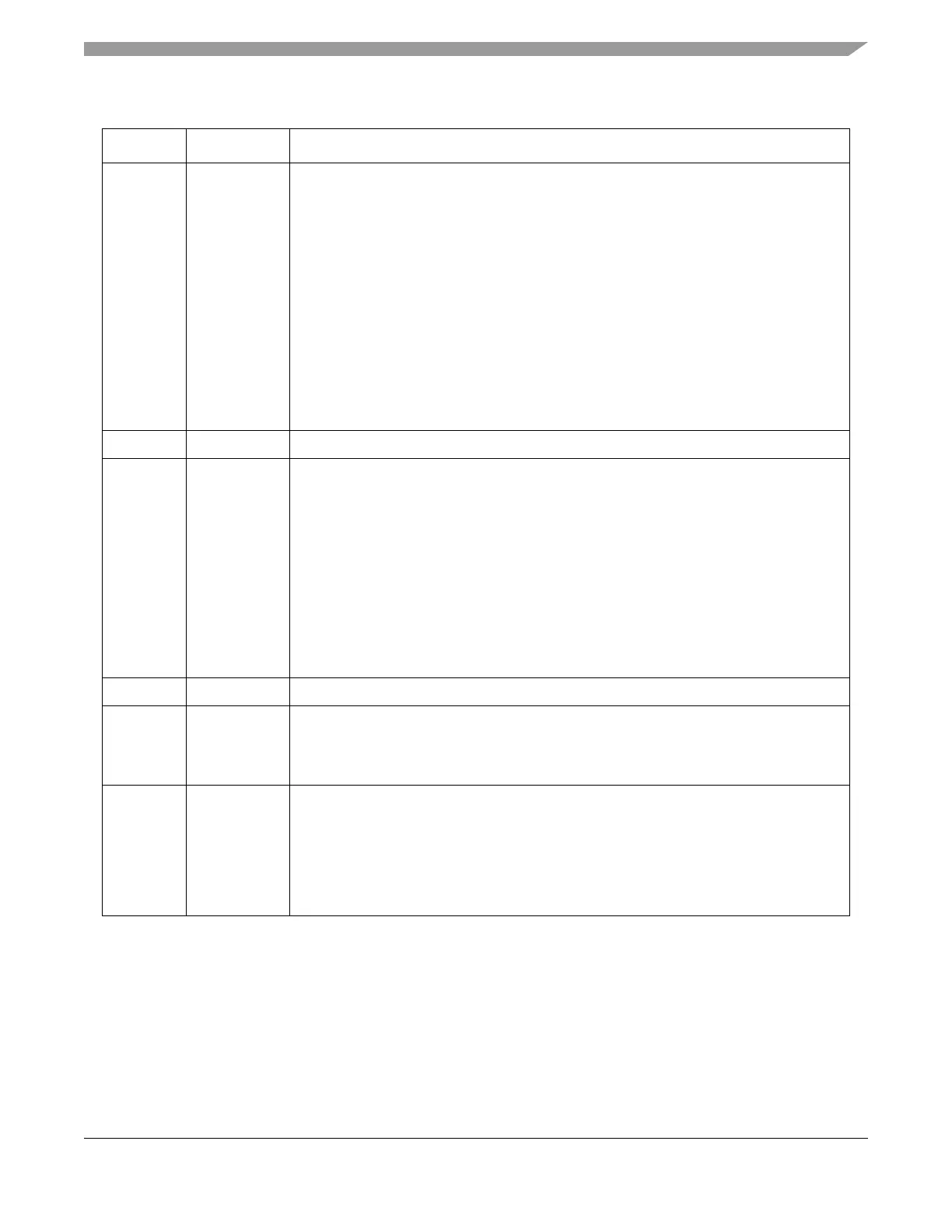

12 RFOFn RFIFO overflow flag n. Indicates an overflow event on RFIFOn. RFOFn is set when

RFIFOn is already full, and a new data is received from the on-chip ADCs or from the

external device. The RFIFOn will not overwrite older data in the RFIFO, and the new data

will be ignored. When RFOIEn (see Section 19.3.2.7) and RFOFn are both asserted, the

eQADC generates an interrupt request.

Apart from generating an independent interrupt request for an RFIFOn overflow event, the

eQADC also provides a combined interrupt at which the result FIFO overflow interrupt, the

command FIFO underflow interrupt, and the command FIFO trigger overrun interrupt

requests of all CFIFOs are ORed. When RFOIEn, CFUIEn, and TORIEn are all asserted,

this combined interrupt request is asserted whenever one of the following 18 flags

becomes asserted: RFOFn, CFUFn, and TORFn (assuming that all interrupts are

enabled). See Section 19.4.7, “eQADC eDMA/Interrupt Request,” for details.

Write 1 to clear RFOFn. Writing a 0 has no effect.

0 No RFIFO overflow event occurred.

1 An RFIFO overflow event occurred.

13 — Reserved.

14 RFDFn RFIFO drain flag n. Indicates if RFIFOn has valid entries that can be drained or not. RFDFn

is set when the RFIFOn has at least one valid entry in it. When RFDEn (see Section

19.3.2.7) and RFDFn are both asserted, an interrupt or an eDMA request will be generated

depending on the status of the RFDSn bit. When RFDSn is negated (interrupt requests

selected), software clears RFDFn by writing a 1 to it. Writing a 0 has no effect. When

RFDSn is asserted (eDMA requests selected), RFDFn is automatically cleared by the

eQADC when the RFIFO becomes empty.

0 RFIFOn is empty.

1 RFIFOn has at least one valid entry.

Note: In the interrupt service routine, RFDF must be cleared only after the RFIFOn pop

register is read.

Note: RFDFn should not be cleared when RFDS

n is asserted (eDMA requests selected).

15 — Reserved.

16–19 CFCTRn

[0:3]

CFIFOn entry counter. Indicates the number of commands stored in the CFIFOn. When

the eQADC completes transferring a piece of new data from the CFIFOn, it decrements

CFCTRn by 1. Writing a word or any bytes to the corresponding CFIFO Push Register (see

Section 19.3.2.4) increments CFCTRn by 1. Writing any value to CFCTRn has no effect.

20–23 TNXTPTRn

[0:3]

CFIFOn transfer next pointer. Indicates the index of the next entry to be removed from

CFIFOn when it completes a transfer. When TNXTPTRn is 0, it points to the entry with the

smallest memory-mapped address inside CFIFOn. TNXTPTRn is only updated when a

command transfer is completed. If the maximum index number (CFIFO depth minus 1) is

reached, TNXTPTRn is wrapped to 0, else, it is incremented by 1. For details refer to

Section 19.4.3.1, “CFIFO Basic Functionality.” Writing any value to TNXTPTRn has no

effect.

Table 19-12. EQADC_FISRn Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...