MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-93

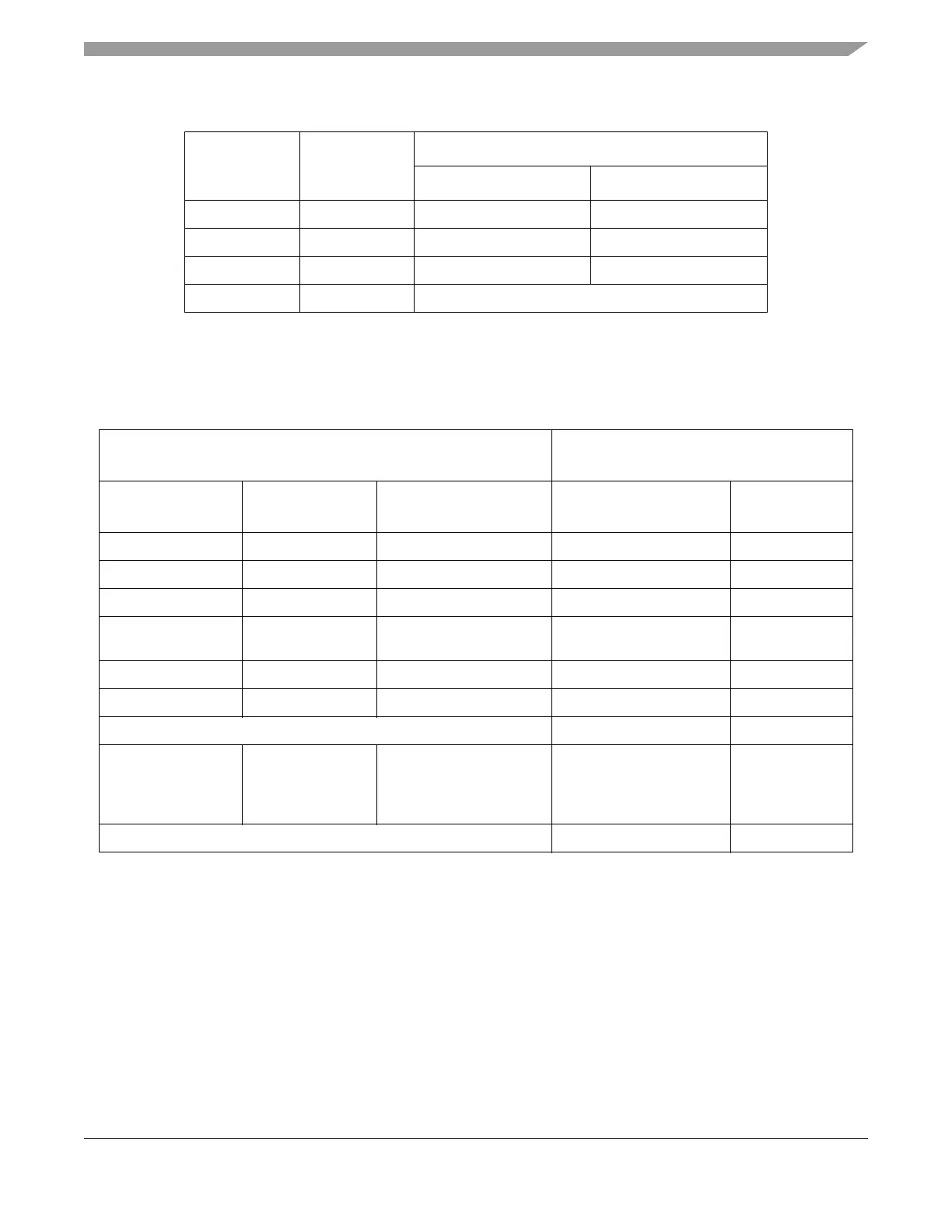

Table 19-51 shows the channel number assignments for the non-multiplexed mode. The 40 single-ended

channels and 4 differential pairs are shared between the two ADCs.

Figure 19-52 shows the channel number assignments for multiplexed mode. The ADC with the

ADCn_EMUX bit asserted can access 4 differential pairs, 39 single-ended, and, at most, 32 externally

multiplexed channels. Refer to Section 19.4.6.2, “External Multiplexing,” for a detailed explanation about

how external multiplexing can be achieved.

Table 19-50. ADCn_EMUX Bits Combinations

ADC0_EMUX ADC1_EMUX

CHANNEL_NUMBER should be set as in

ADC0 ADC1

00Refer to Table 19-51 Refer to Table 19-51

01Refer to Table 19-51 Refer to Figure 19-52

10Refer to Figure 19-52 Refer to Table 19-51

1 1 Reserved

1

1

ADC0_EMUX and ADC1_EMUX must not be asserted at the same time.

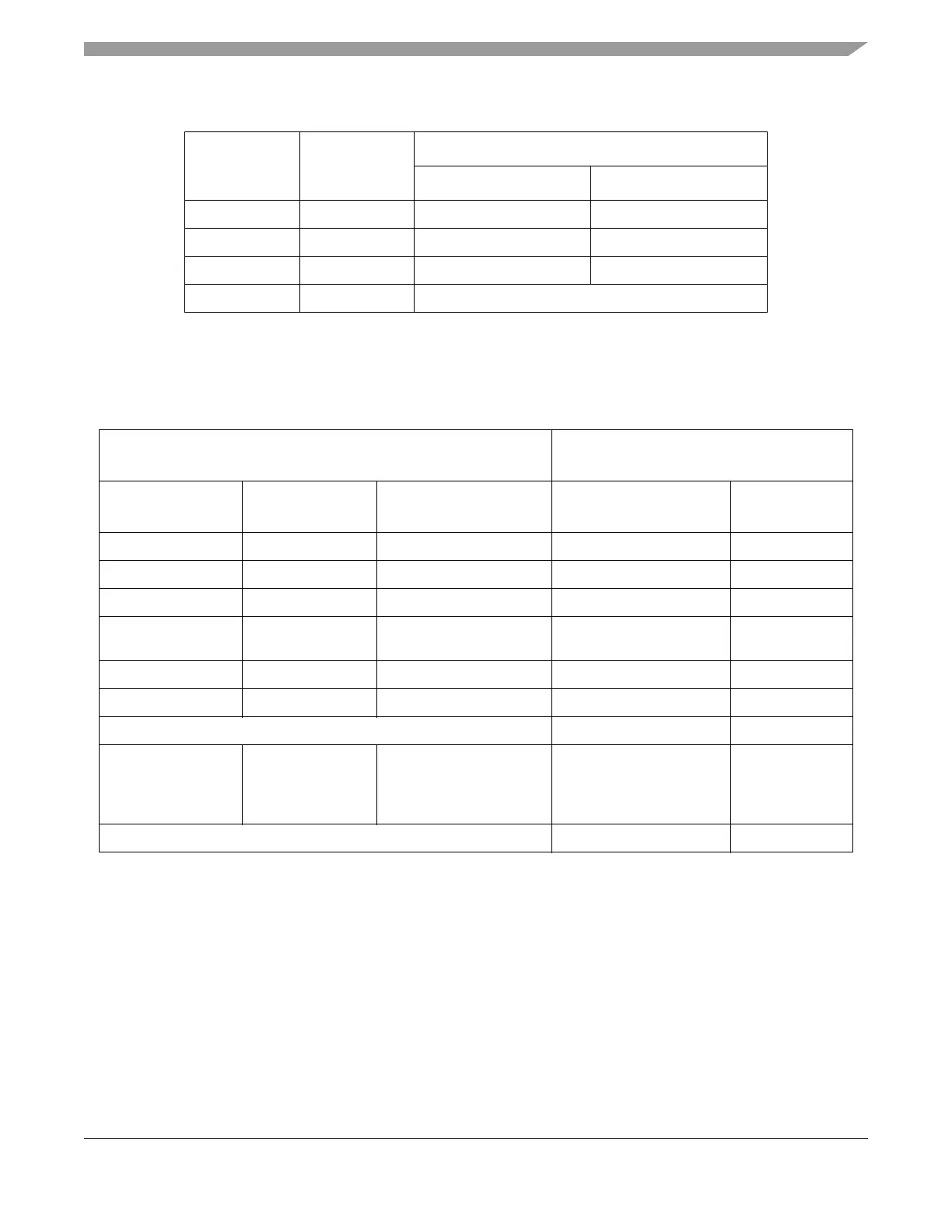

Table 19-51. Non-multiplexed Channel Assignments

1

1

The two on-chip ADCs can access the same analog input pins but simultaneous conversions are not allowed. Also, when

one ADC is performing a differential conversion on a pair of pins, the other ADC must not access either of these two pins

as single-ended channels.

Input Pins

Channel Number in

CHANNEL_NUMBER Field

Analog

Pin Name

Other

Functions

Conversion Type Binary Decimal

AN0 to AN39 Single-ended 0000_0000 to 0010_0111 0 to 39

VRH Single-ended 0010_1000 40

VRL Single-ended 0010_1001 41

(VRH - VRL)/2

see footnote

2

2

This equation only applies before calibration. After calibration, the 50% reference point will actually return approximately

20mV lower than the expected 50% of the difference between the High Reference Voltage (VRH) and the Low Reference

Voltage (VRL). For calibration of the ADC only the 25% and 75% points should be used as described in Section 19.5.6.1,

“MAC Configuration Procedure”

Single-ended 0010_1010 42

75% x (VRH - VRL) Single-ended 0010_1011 43

25% x (VRH - VRL) Single-ended 0010_1100 44

Reserved 0010_1101 to 0101_1111 45 to 95

DAN0+ and DAN0-

DAN1+ and DAN1-

DAN2+ and DAN2-

DAN3+ and DAN3-

Differential

Differential

Differential

Differential

0110_0000

0110_0001

0110_0010

0110_0011

96

97

98

99

Reserved 0110_0100 to 1111_1111 100 to 255

Loading...

Loading...