MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

20-12 Freescale Semiconductor

In master mode, the DSPIx_CTARn registers define combinations of transfer attributes such as frame size,

clock phase and polarity, data bit ordering, baud rate, and various delays. In slave mode, a subset of the bit

fields in the DSPIx_CTAR0 and DSPIx_CTAR1 registers are used to set the slave transfer attributes. See

the individual bit descriptions for details on which bits are used in slave modes.

When the DSPI is configured as an SPI master, the CTAS field in the command portion of the TX FIFO

entry selects which of the DSPIx_CTAR registers is used on a per-frame basis. When the DSPI is

configured as an SPI bus slave, the DSPIx_CTAR0 register is used.

When the DSPI is configured as a DSI master, the DSICTAS field in the DSPI DSI configuration register

(DSPIx_DSICR) selects which of the DSPIx_CTAR register is used. For more information on the

DSPIx_DSICR see Section 20.3.2.10, “DSPI DSI Configuration Register (DSPIx_DSICR).” When the

DSPI is configured as a DSI bus slave, the DSPIx_CTAR1 register is used.

In CSI configuration, the transfer attributes are selected based on whether the current frame is SPI data or

DSI data. SPI transfers in CSI configuration follow the protocol described for SPI configuration, and DSI

transfers in CSI configuration follow the protocol described for DSI configuration. CSI configuration is

only valid in conjunction with master mode. See Section 20.4.5, “Combined Serial Interface (CSI)

Configuration” for more details.

.

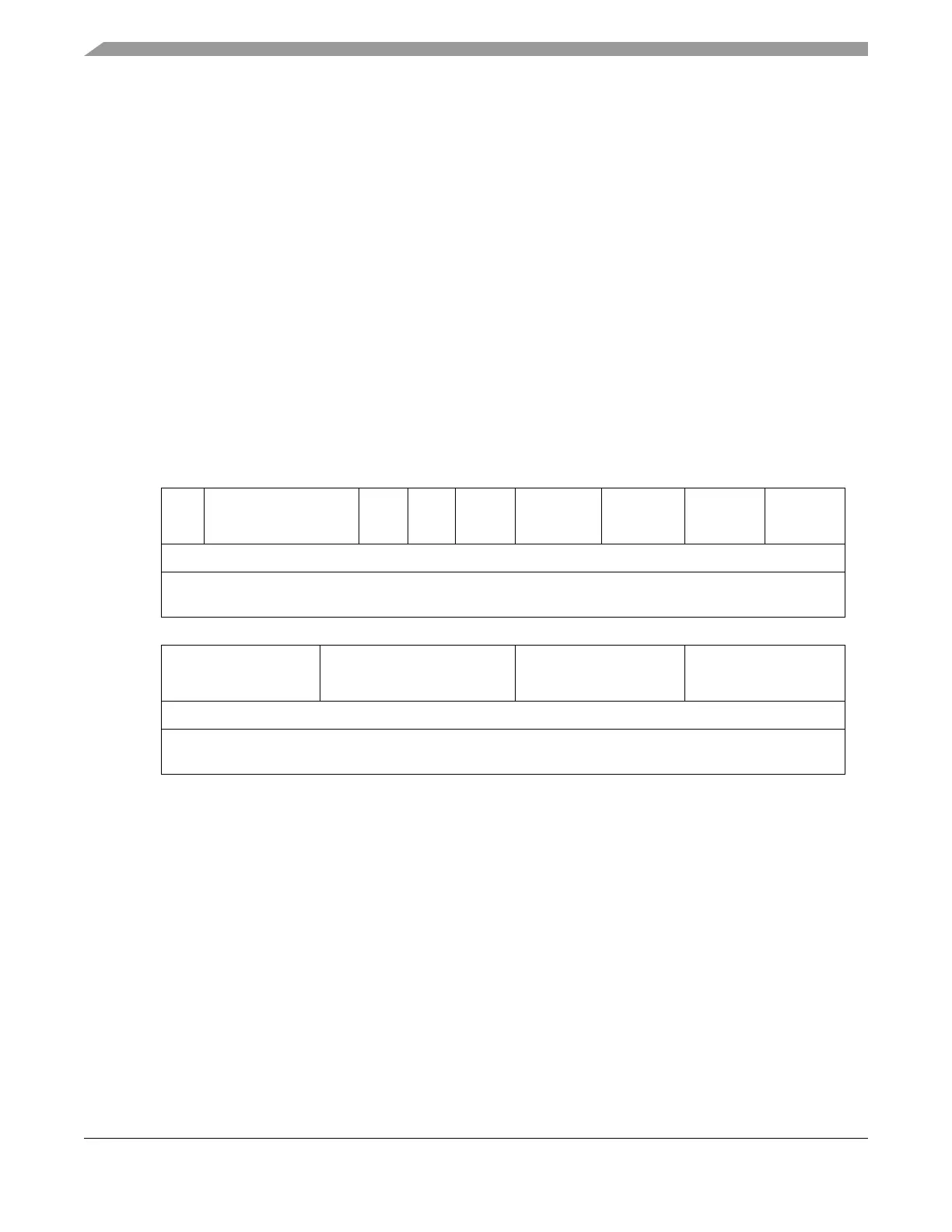

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R DBR FMSZ CPOL CPHA LSBFE PCSSCK PASC PDT PBR

W

Reset01111 0 0 0 0 0 0 00000

Reg

Addr

Base + 0x000C (DSPIx_CTAR0); 0x0010 (DSPIx_CTAR1); 0x0014 (DSPIx_CTAR2); 0x0018 (DSPIx_CTAR3);

0x001C (DSPIx_CTAR4); 0x0020 (DSPIx_CTAR5); 0x0024 (DSPIx_CTAR6); 0x0028 (DSPIx_CTAR7)

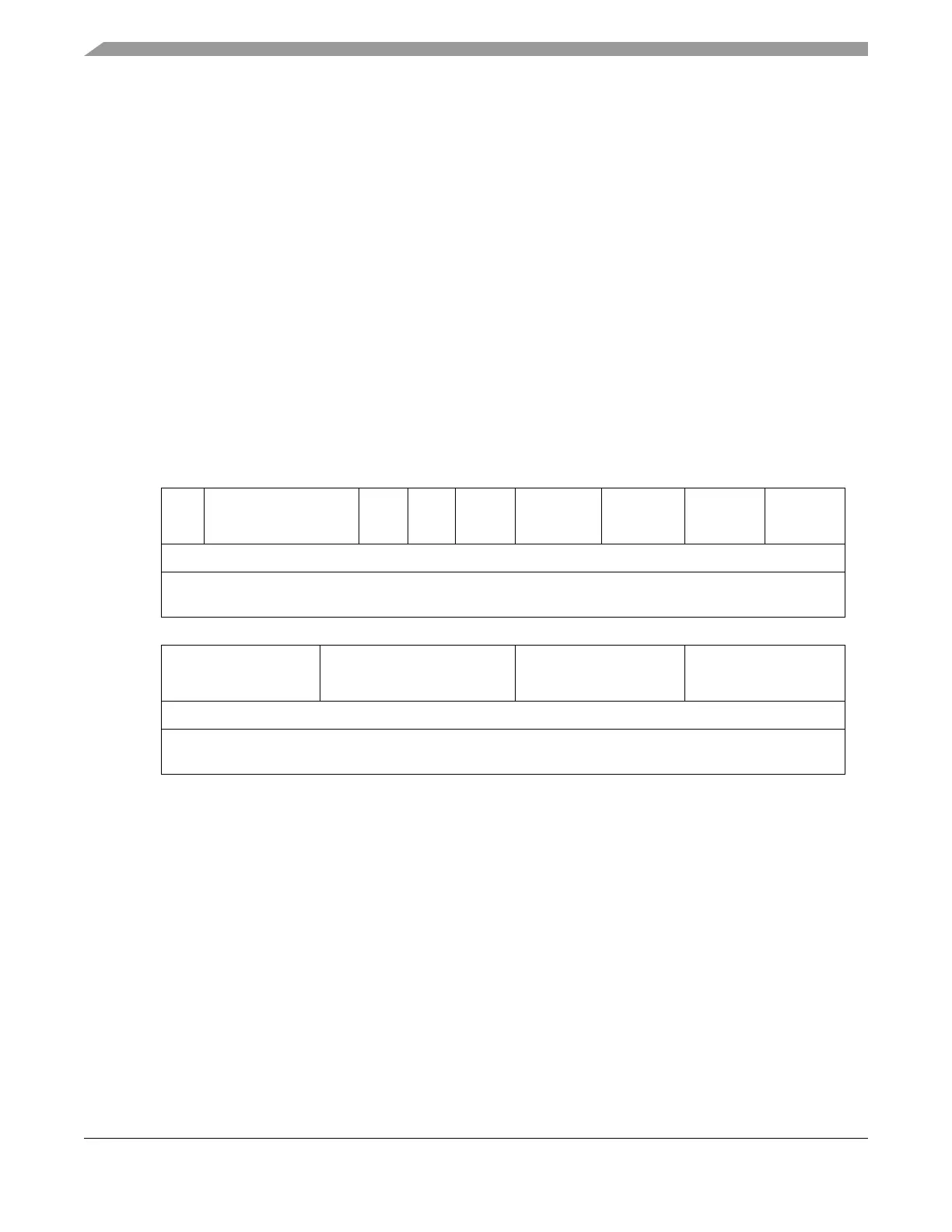

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R CSSCK ASC DT BR

W

Reset00000 0 0 0 0 0 0 00000

Reg

Addr

Base + 0x000C (DSPIx_CTAR0); 0x0010 (DSPIx_CTAR1); 0x0014 (DSPIx_CTAR2); 0x0018 (DSPIx_CTAR3);

0x001C (DSPIx_CTAR4); 0x0020 (DSPIx_CTAR5); 0x0024 (DSPIx_CTAR6); 0x0028 (DSPIx_CTAR7)

Figure 20-5. DSPI Clock and Transfer Attributes Registers 0–7 (DSPIx_CTARn)

Loading...

Loading...