MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-13

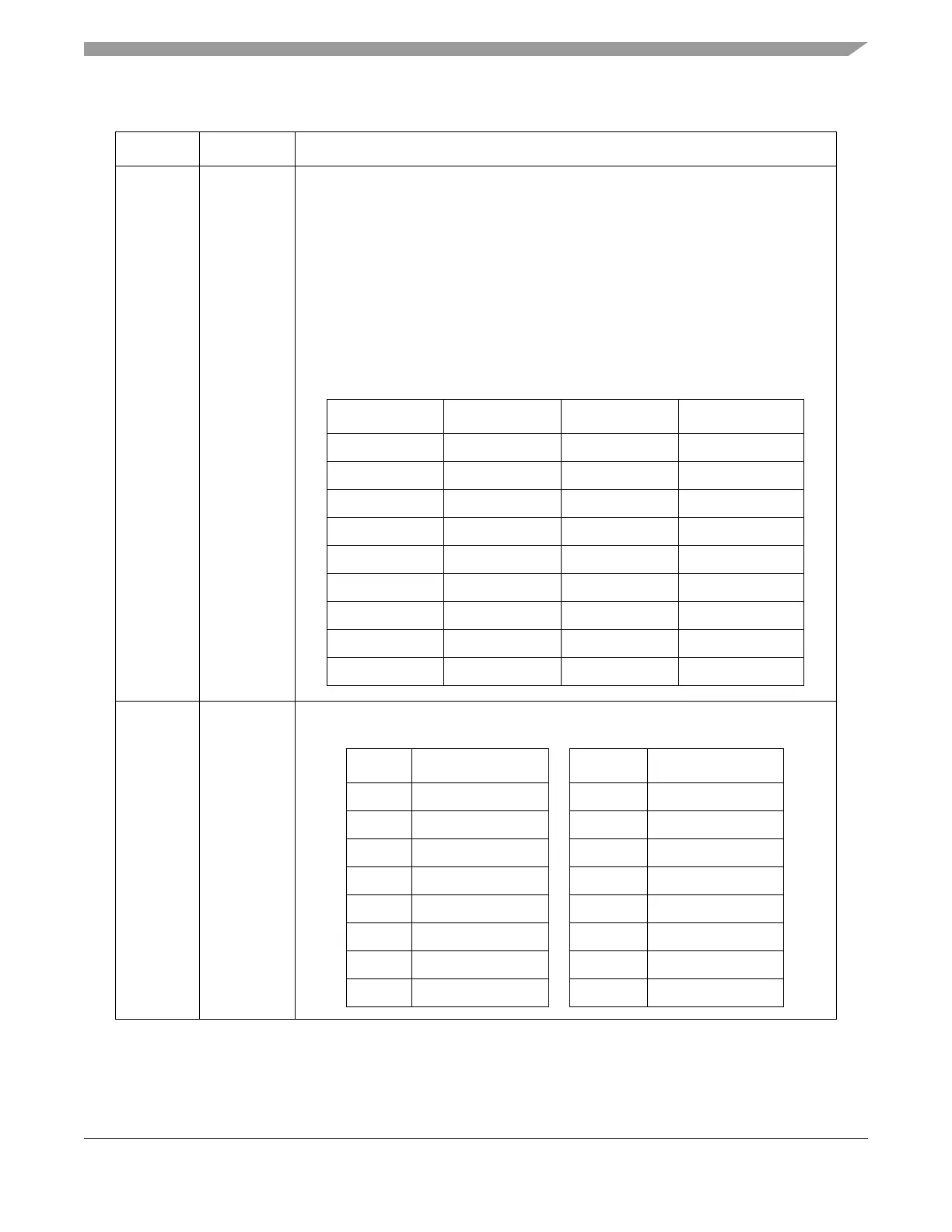

Table 20-5. DSPIx_CTARn Field Description

Bits Name Description

0 DBR Double baud rate.

The DBR bit doubles the effective baud rate of the serial communications clock (SCK).

This field is only used in master mode. It effectively halves the baud rate division ratio

supporting faster frequencies and odd division ratios for the serial communications

clock (SCK). When the DBR bit is set, the duty cycle of the serial communications clock

(SCK) depends on the value in the baud rate prescaler and the clock phase bit as listed

below. See the BR field below and Section 20.4.6.1, “Baud Rate Generator” for details

on how to compute the baud rate. If the overall baud rate is divide by two or divide by

three of the system clock then the continuous SCK enable or the modified timing format

enable bits must not be set.

0 The baud rate is computed normally with a 50/50 duty cycle

1 Baud rate is doubled with the duty cycle depending on the baud rate prescaler

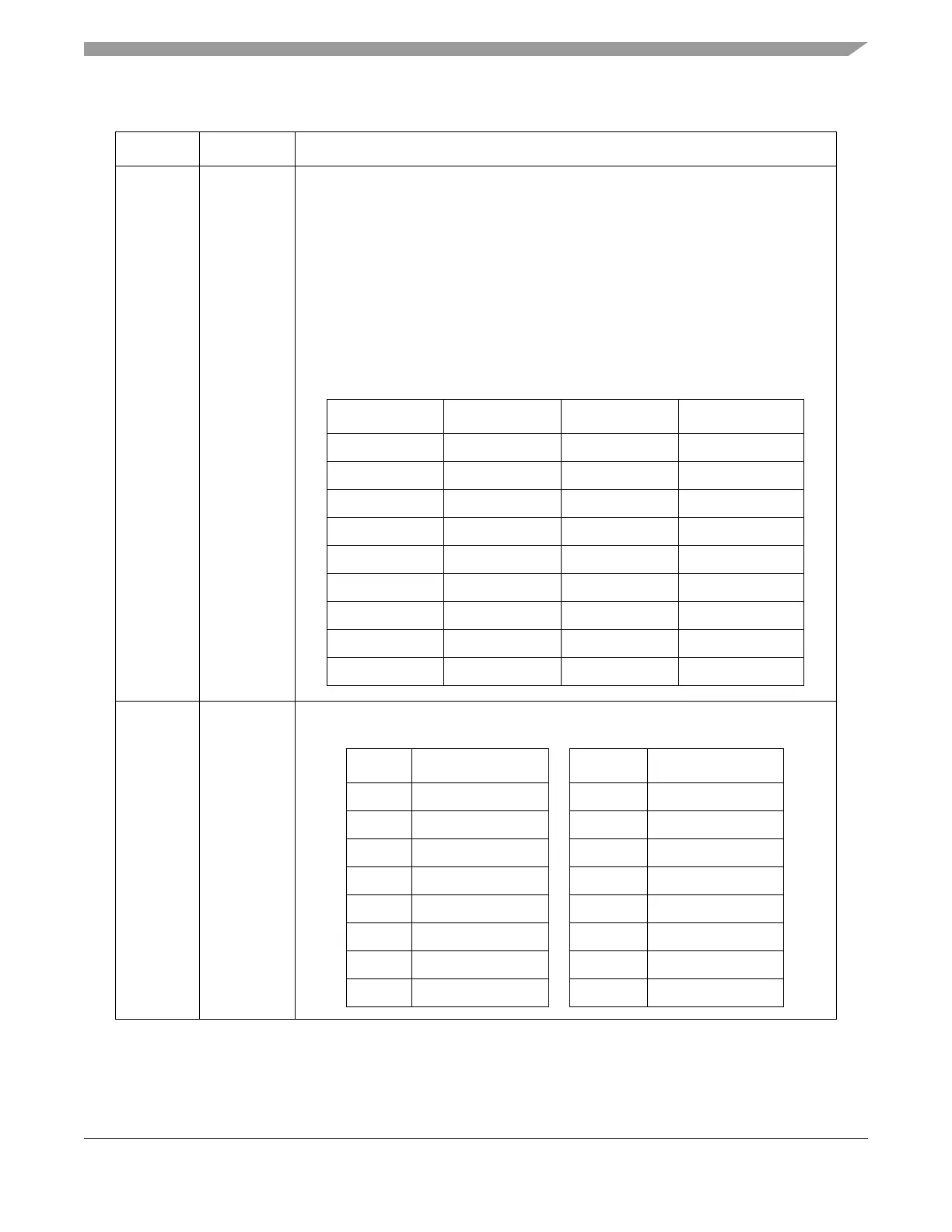

1–4 FMSZ

[0:3]

FMSZ. Selects the number of bits transferred per frame. The FMSZ field is used in

master mode and slave mode. The table below lists the frame sizes.

DBR CPHA PBR SCK Duty Cycle

0 any any 50/50

100050/50

100133/66

101040/60

101143/57

110050/50

110166/33

111060/40

111157/43

FMSZ Framesize FMSZ Framesize

0000 Reserved 1000 9

0001 Reserved 1001 10

0010 Reserved 1010 11

0011 4 1011 12

0100 5 1100 13

0101 6 1101 14

0110 7 1110 15

0111 8 1111 16

Loading...

Loading...