MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-51

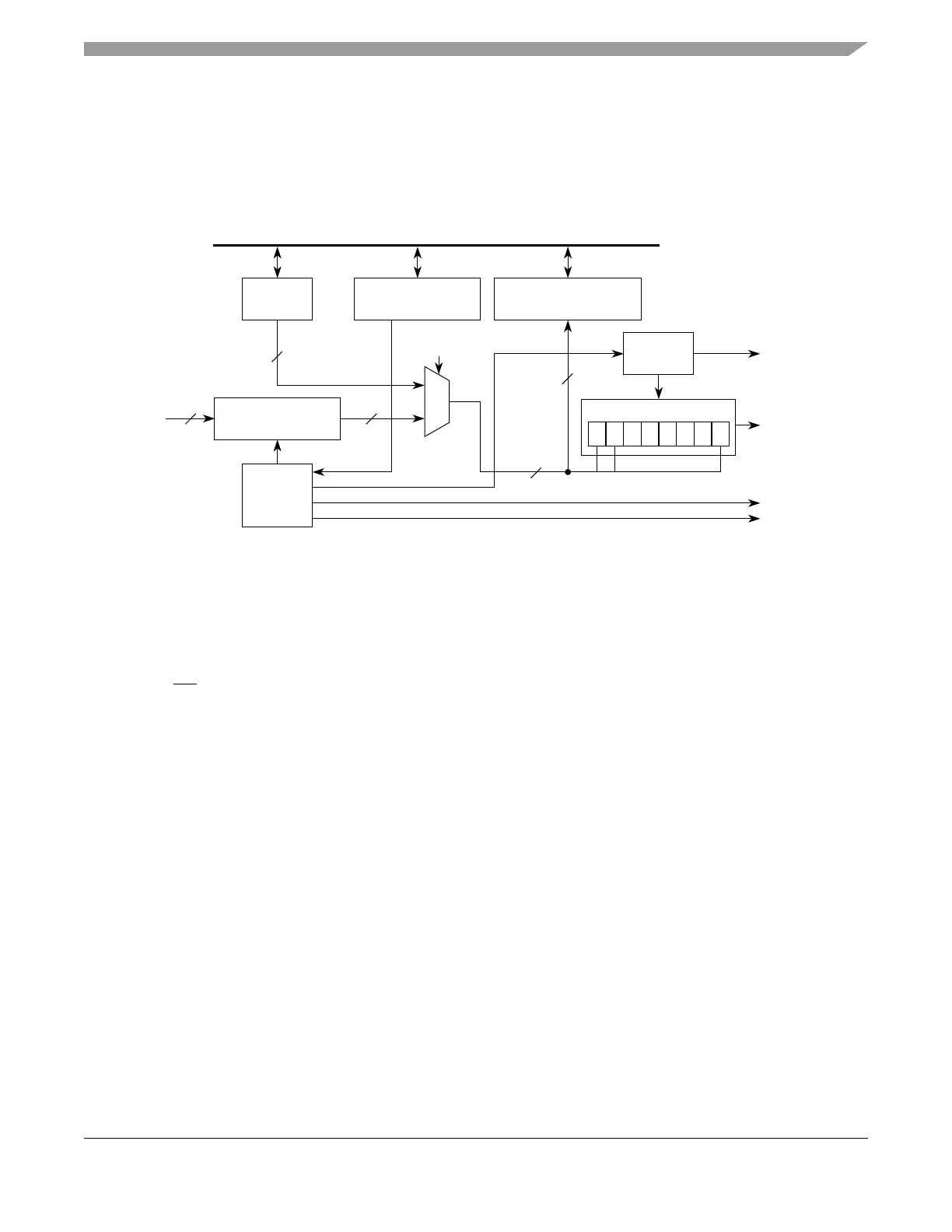

20.4.5.1 CSI Serialization

Serialization in the CSI configuration is similar to serialization in DSI configuration. The transfer

attributes for SPI frames are determined by the DSPIx_CTAR selected by the CTAS field in the SPI

command halfword. The transfer attributes for the DSI frames are determined by the DSPIx_CTAR

selected by the DSICTAS field in the DSPIx_DSICR. Figure 20-32 shows the CSI serialization logic.

Figure 20-32. CSI Serialization Diagram

The parallel inputs signal states are latched into the DSPIx_SDR on the rising edge of every system clock

and serialized based on the transfer initiation control settings in the DSPIx_DSICR. For more information

on the DSPIx_SDR, refer to Section 20.3.2.11, “DSPI DSI Serialization Data Register (DSPIx_SDR).”

SPI frames written to the TX FIFO have priority over DSI data from the DSPIx_SDR and are transferred

at the next frame boundary. A copy of the most recently transferred DSI frame is stored in the

DSPIx_COMPR. The transfer priority logic selects the source of the serialized data and asserts the

appropriate CS signal.

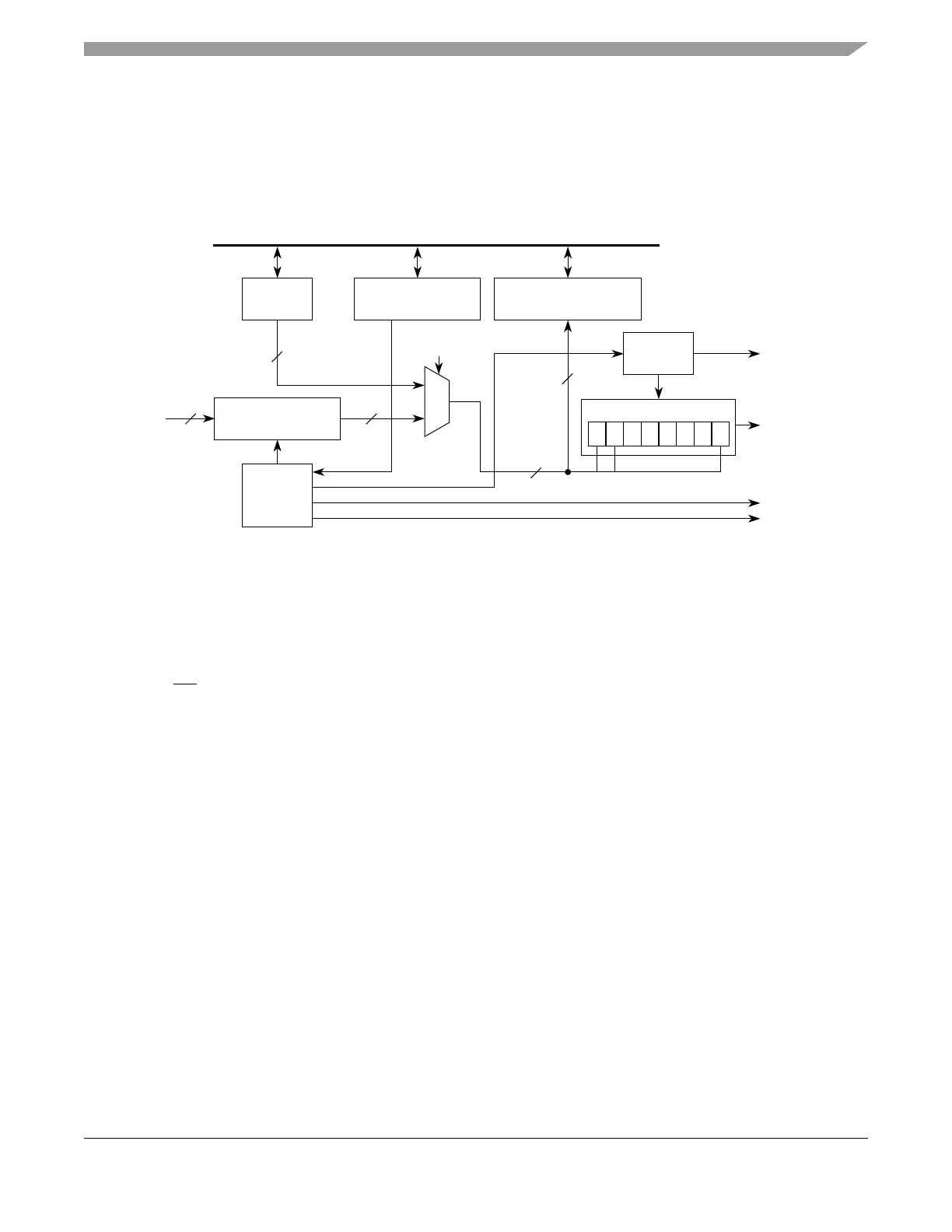

20.4.5.2 CSI Deserialization

The deserialized frames in CSI configuration go into the DSPIx_SDR or the RX FIFO based on the transfer

priority logic. When DSI frames are transferred the returned frames are deserialized and latched into the

DSPIx_DDR. When SPI frames are transferred the returned frames are deserialized and written to the RX

FIFO. Figure 20-33 shows the CSI deserialization logic.

SOUT

Parallel

DSI Control

Register

DSI Transmit

Comparison Register

Clock

Logic

0 1 • • • • • 15

Shift Register

DSI Serialization

Data Register

Control

Logic

SCK

Inputs

PCSx (SPI)

PCSy (DSI)

16

16

16

16

Transfer

Slave Bus Interface

16

TX FIFO

(P_IN)

Priority Logic

Loading...

Loading...