MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 21-9

21.3.3.3 eSCI Data Register (ESCIx_DR)

NOTES

In 8-bit data format, only bits 8–15 of ESCIx_DR need to be accessed.

When transmitting in 9-bit data format and using 8-bit write instructions,

write first to ESCIx_DR[0–7], then ESCIx_DR[8–15]. For 9-bit

transmissions, a single write may also be used.

ESCIx_DR should not be used in LIN mode, writes to this register are

blocked in LIN mode.

Even if parity generation/checking is enabled via ESCIx_CR[PE], the parity

bit will not be masked out.

21.3.3.4 eSCI Status Register (ESCIx_SR)

The ESCIx_SR indicates the current status. The status flags can be polled, and some can also be used to

generate interrupts. All bits in ESCIx_SR except for RAF are cleared by writing 1 to them.

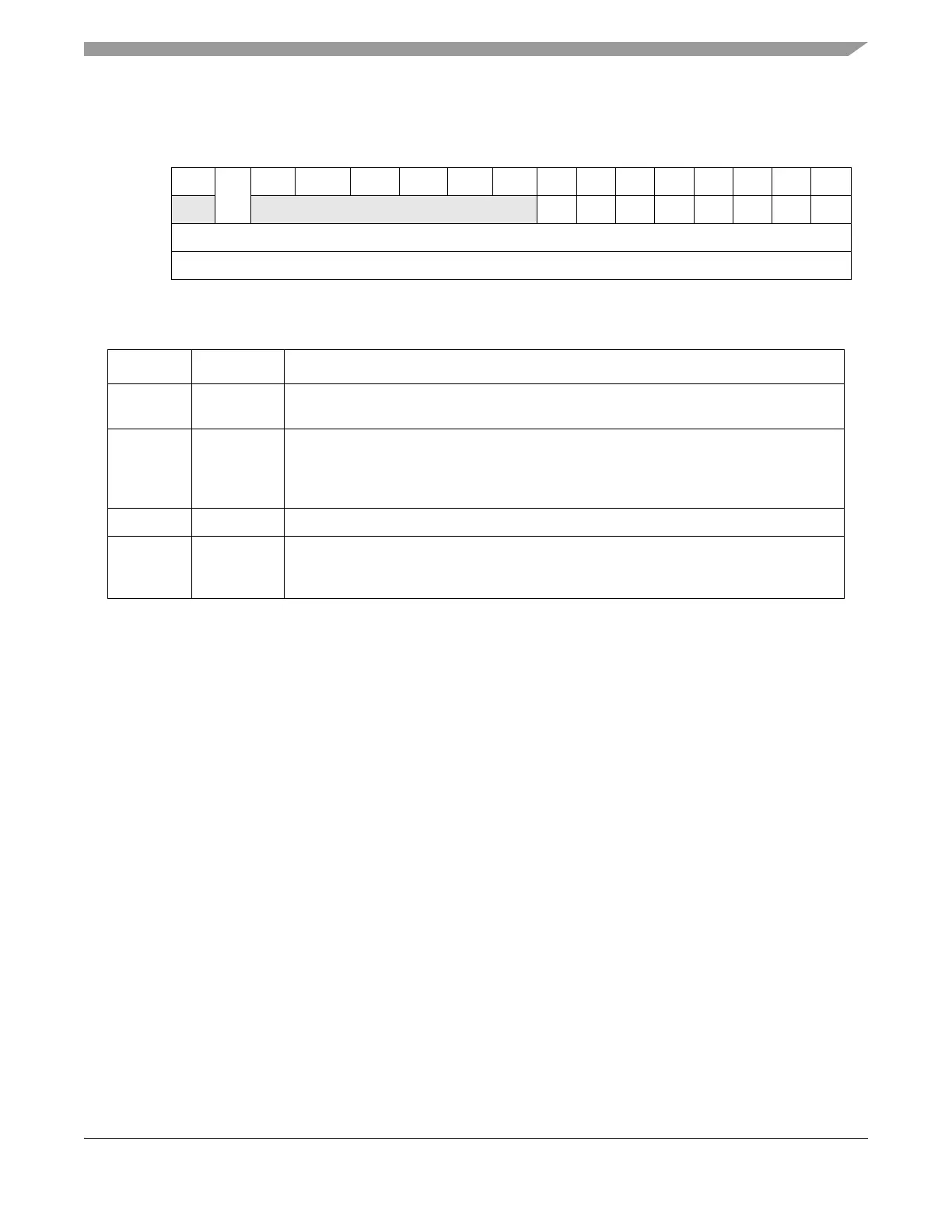

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

RR8T8 0 0 0 0 0 0 R7R6R5R4R3R2R1R0

W T7 T6 T5 T4 T3 T2 T1 T0

Reset000 0 0 0 0 0 00000000

Reg Addr Base + 0x0006

Figure 21-4. eSCI Data Register (ESCIx_DR)

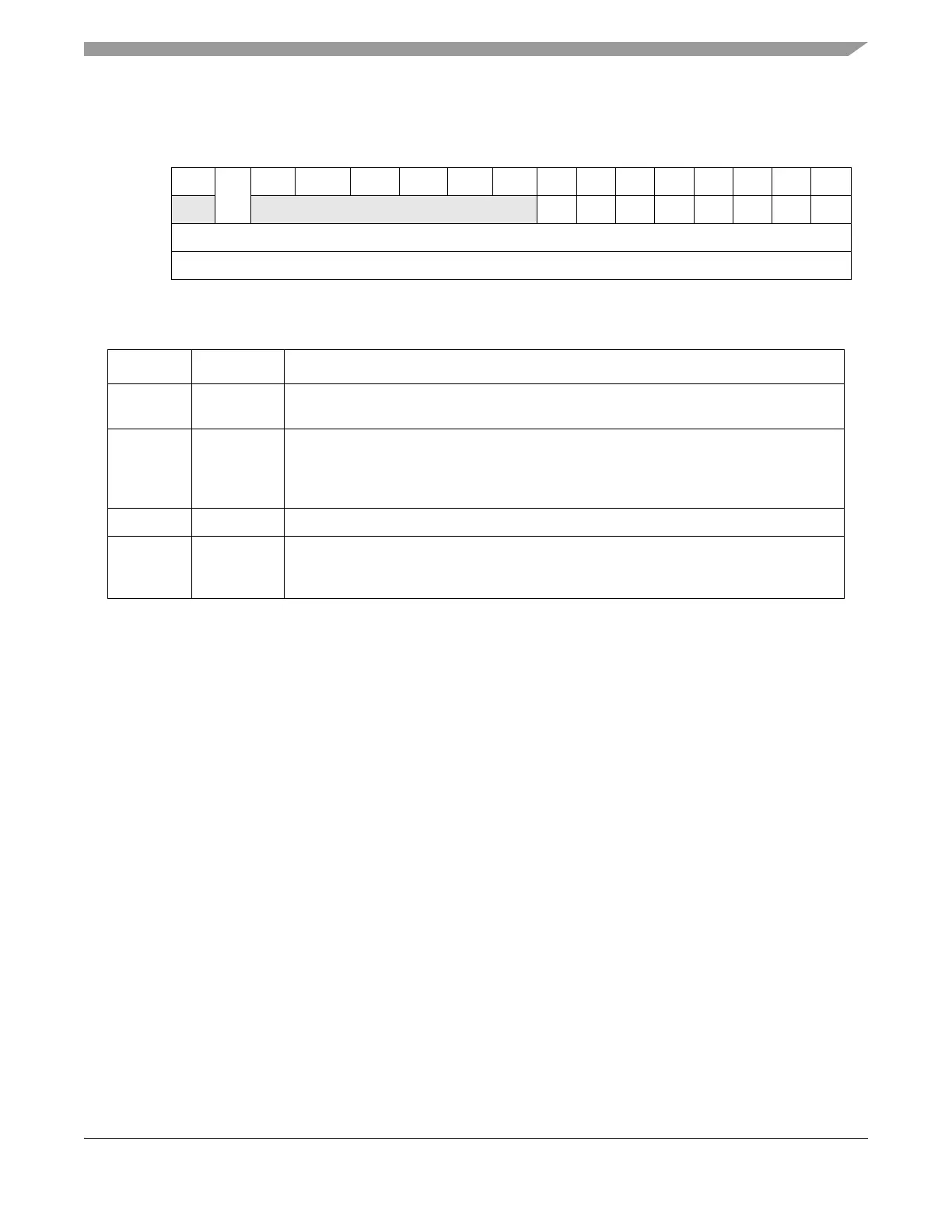

Table 21-5. ESCIx_DR Field Description

Bits Name Description

0 R8 Received bit 8. R8 is the ninth data bit received when the eSCI is configured for 9-bit data

format (M = 1).

1 T8 Transmit bit 8. T8 is the ninth data bit transmitted when the eSCI is configured for 9-bit data

format (M = 1).

Note: If the value of T8 is the same as in the previous transmission, T8 does not have to

be rewritten.The same value is transmitted until T8 is rewritten.

2–7 — Reserved.

8–15 R7–R0 /

T7–T0

Received bits/transmit bits 7–0 for 9-bit or 8-bit formats. Bits 7–0 from SCI communication

may be read from ESCIx_DR[8–15] (provided that SCI communication was successful).

Writing to ESCIx_DR [8–15] provides bits 7–0 for SCI transmission.

Loading...

Loading...