MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 21-13

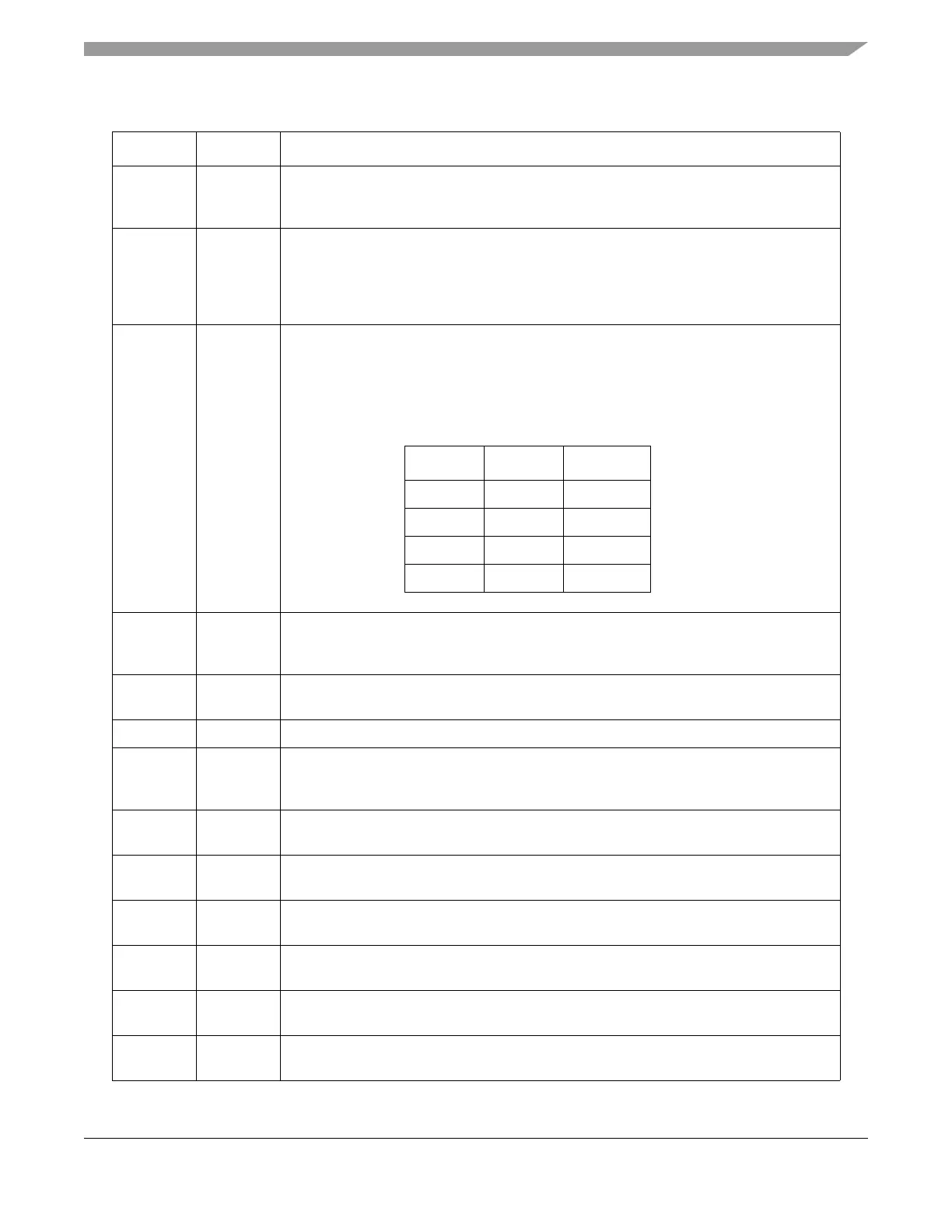

Table 21-7. ESCIx_LCR Field Descriptions

Bits Name Description

0 LRES LIN resynchronize. Causes the LIN protocol engine to return to start state. This happens

automatically after bit errors, but software may force a return to start state manually via this

bit. The bit first must be set then cleared, so that the protocol engine is operational again.

1 WU LIN bus wake-up. Generates a wake-up signal on the LIN bus. This must be set before a

transmission, if the bus is in sleep mode. This bit will auto-clear, so a read from this bit will

always return 0.

According to LIN 2.0, generating a valid wake-up character requires programming the SCI

baud rate to a range of 32K baud down to 1.6K baud.

2–3 WUD

[0:1]

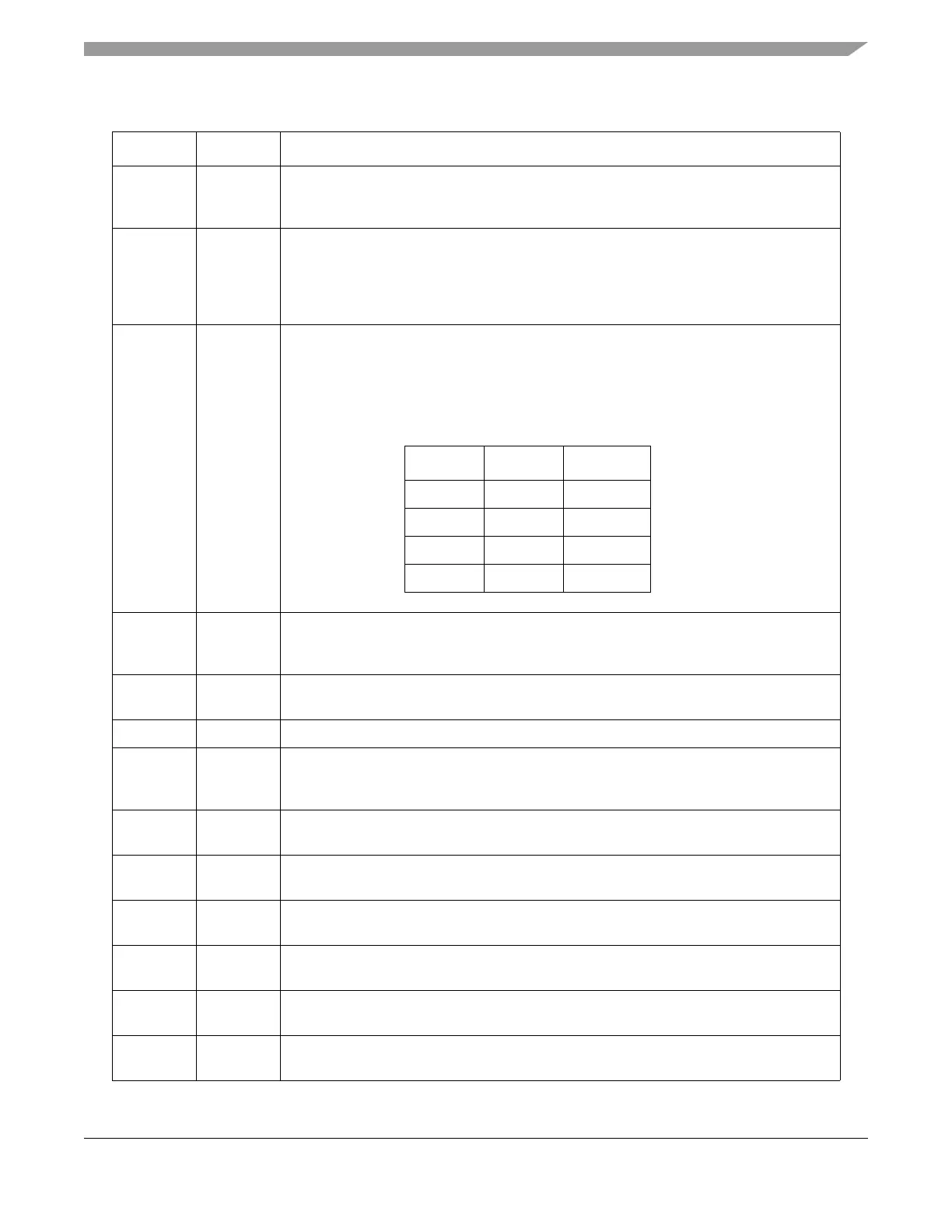

Wake-up delimiter time. Determines how long the LIN engine waits after generating a

wake-up signal, before starting a new frame. The eSCI will not set ESCIx_SR[TXRDY]

before this time expires. Note that in addition to this delimiter time, the CPU and the eSCI

will require some setup time to start a new transmission and typically there is an additional

bit time delay. The table below shows how the values for WUD0 and WUD1 affect the

delimiter time.

4 LDBG LIN debug mode. Prevents the LIN FSM from automatically resetting, after an exception

(bit error, physical bus error, wake-up flag) has been received. This is for debug purposes

only.

5 DSF Double stop flags. When a bit error has been detected, this will add an additional stop flag

to the byte in which the error occurred.

6 PRTY Activating parity generation. Generate the two parity bits in the LIN header.

7 LIN LIN mode. Switch device into LIN mode.

0 LIN disabled

1 LIN enabled

8 RXIE LIN RXREG ready interrupt enable. Generates an Interrupt when new data is available in

the LIN RXREG. For a list of interrupt enables and flags, see Table 21-21.

9 TXIE LIN TXREG ready interrupt enable. Generates an Interrupt when new data can be written

to the LIN TXREG. For a list of interrupt enables and flags, see Table 21-21.

10 WUIE RX wake-up interrupt enable. Generates an Interrupt when a wake-up flag from a LIN slave

has been received. For a list of interrupt enables and flags, see Table 21-21.

11 STIE Slave timeout error interrupt enable. Generates an Interrupt when the slave response is too

slow. For a list of interrupt enables and flags, see Table 21-21.

12 PBIE Physical bus error interrupt enable. Generates an Interrupt when no valid message can be

generated on the bus. For a list of interrupt enables and flags, see Tabl e 21 -2 1.

13 CIE CRC error interrupt enable. Generates an Interrupt when a CRC error on a received

extended frame is detected. For a list of interrupt enables and flags, see Table 21-21.

WUD0 WUD1 Bit Times

00 4

01 8

1032

1164

Loading...

Loading...