MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 21-29

For an 8-bit data character, data sampling of the stop bit takes the receiver RT clock 151 clock cycles, as

is shown below:

With the misaligned character shown in Figure 21-19, the receiver counts 151 RT cycles at the point when

the count of the transmitting device is 9 bit times x 16 RT cycles = 147 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 8-bit data

character with no errors is 4.63%, as is shown below:

For a 9-bit data character, data sampling of the stop bit takes the receiver 167 RT cycles, as is shown below:

With the misaligned character shown in Figure 21-19, the receiver counts 167 RT cycles at the point when

the count of the transmitting device is 10 bit times x 16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit

character with no errors is 4.19%, as is shown below:

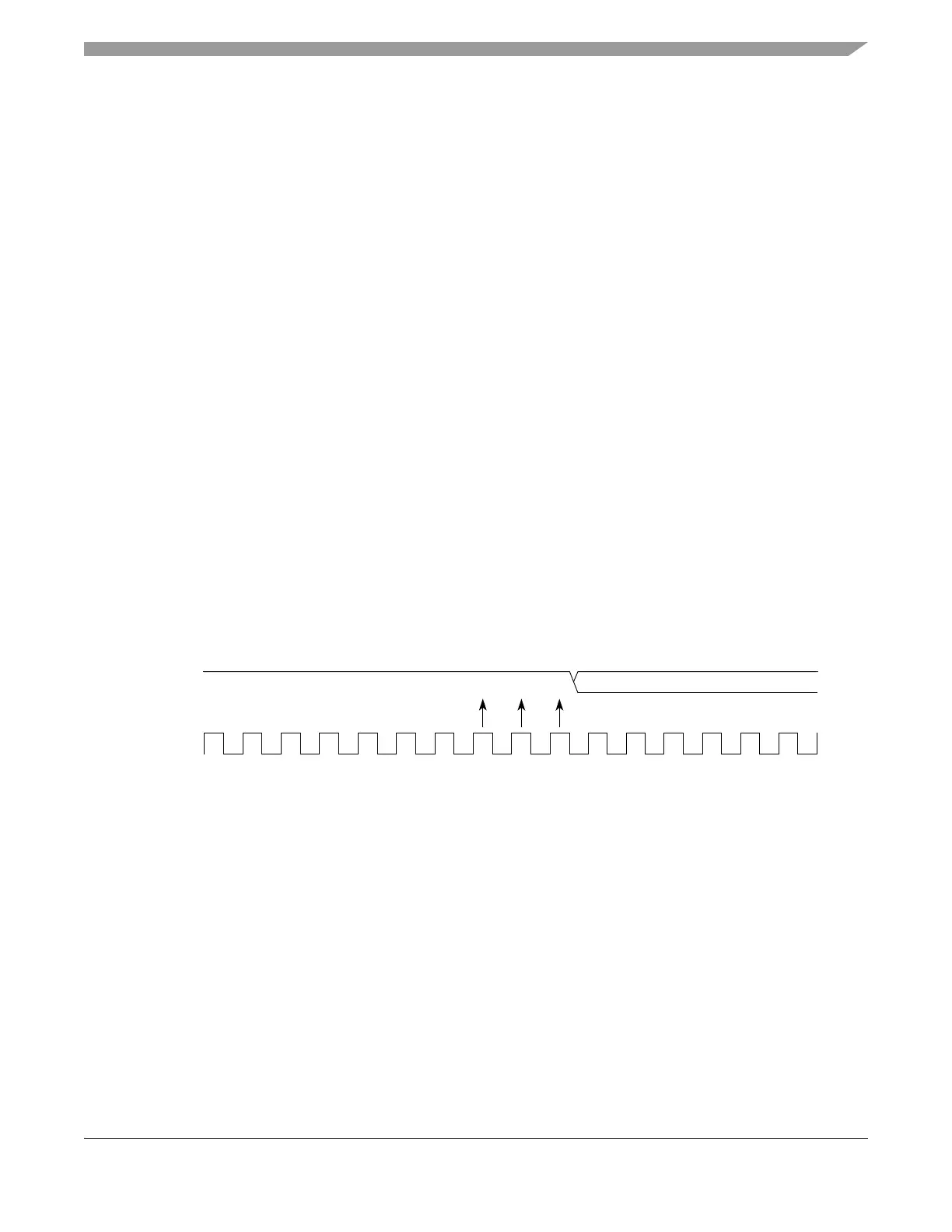

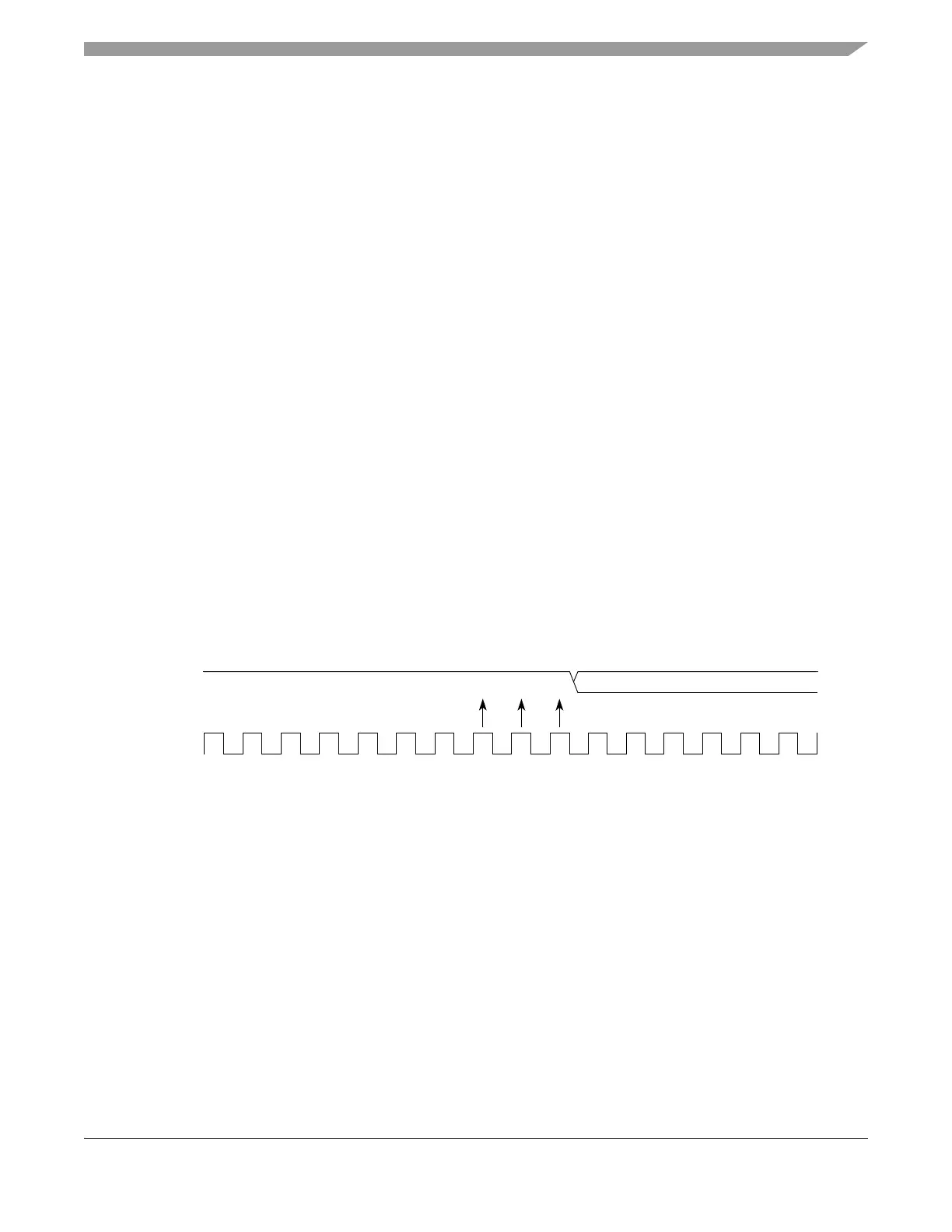

21.4.5.5.2 Fast Data Tolerance

Figure 21-20 shows how much a fast received frame can be misaligned. The fast stop bit ends at RT10

instead of RT16 but is still sampled at RT8, RT9, and RT10.

Figure 21-20. Fast Data

For an 8-bit data character, data sampling of the stop bit takes the receiver 154 RT cycles, as is shown

below:

With the misaligned character shown in Figure 21-20, the receiver counts 154 RT cycles at the point when

the count of the transmitting device is 10 bit times x 16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit

character with no errors is 3.40%, as is shown below:

9 bit times 16 RT cycles 7 RT cycles+ 151 RT cycles=

151 – 144

151

--------------------------

100 4.63%=

10 bit times 16 RT cycles 7 RT cycles+ 167 RT cycles =

167 – 160

167

--------------------------

100 4.19%=

RT1

Receiver

RT Clock

RT2 RT3 RT4 RT5 RT6 RT7 RT8 RT9 RT10 RT11 RT12 RT13 RT14 RT15 RT16

STOP IDLE or Next Frame

Data Samples

9 bit times 16 RT cycles 10 RT cycles+ 154 RT cycles=

160 – 154

160

--------------------------

100 3.40%=

Loading...

Loading...