System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 6-25

6.3.1.12.5 MPC5554: Pad Configuration Registers 28–59 (SIU_PCR28–SIU_PCR59)

NOTE

The MPC5553 register definitions for PCR44 through PCR59 differ from

this MPC5554 register definition. The register definitions for MPC5553

PCR44 through PCR59 are described in the following section.

The SIU_PCR28 through SIU_PCR59 registers control the pin function, direction, and static electrical

attributes of the DATA[0:31]_GPIO[28:59] pins.

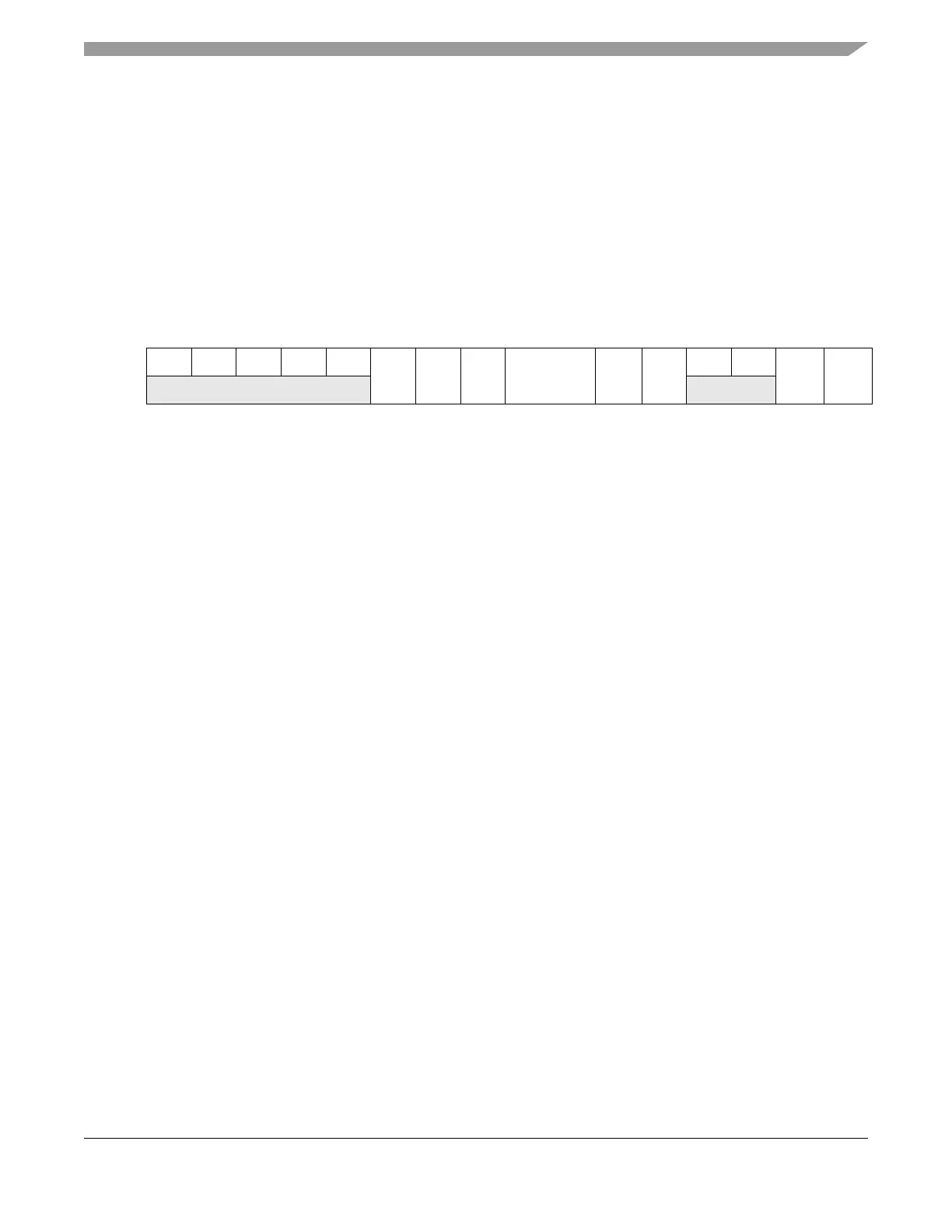

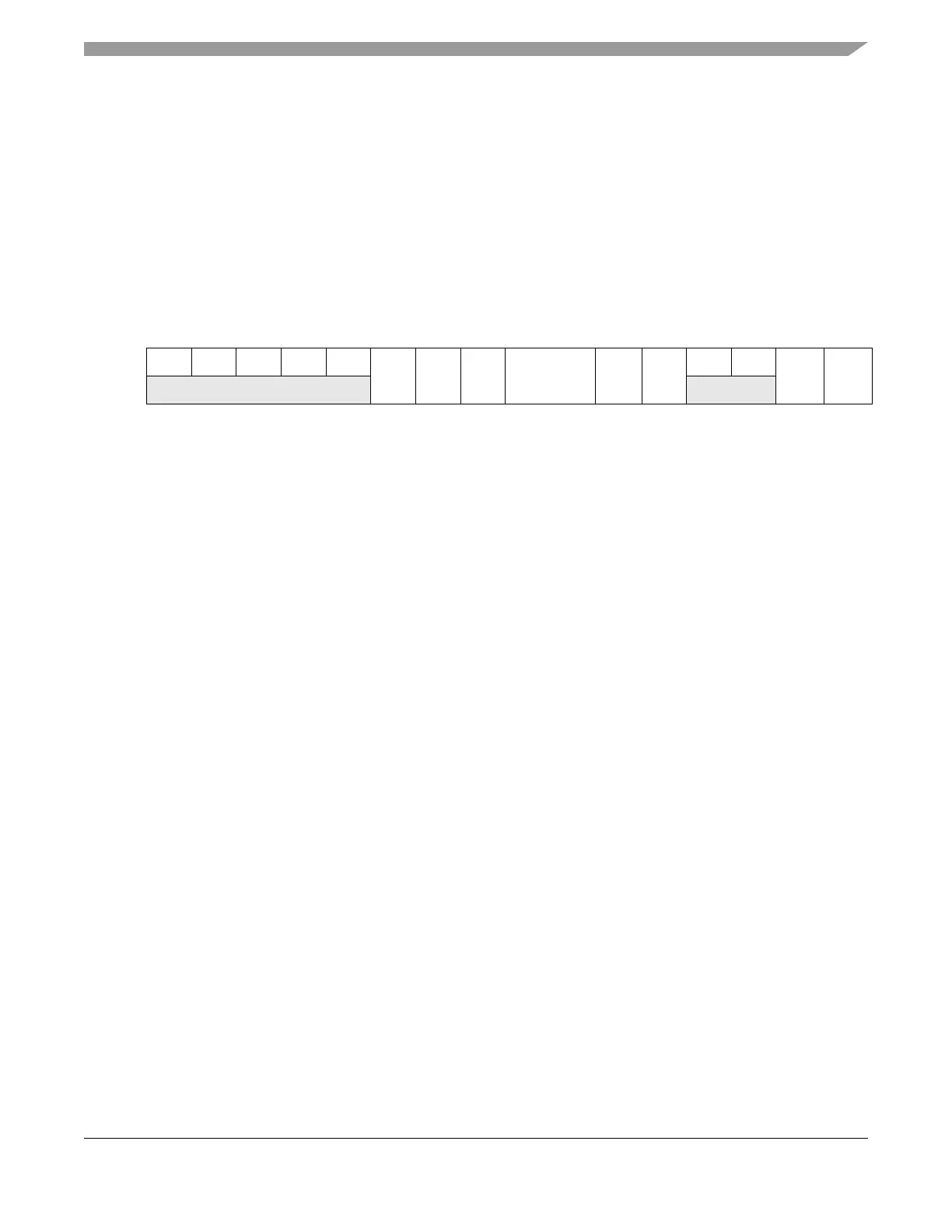

Figure 6-18. DATA[0:31]_GPIO[28:59]

Pad Configuration Registers (SIU_PCR28–SIU_PCR59)

Refer to Table 6-16 for bit field definitions.

Address: Base + 0x0078 through Base + 0x00B6 Access: Read/ write[5:11, 14:15]

0123456789101112131415

R 00000

PA OBE

1

1

When configured as DATA[0:31], the OBE bit has no effect. When configured as GPO, set the OBE bit to 1.

IBE

2

2

When configured as DATA[0:31] or GPO, set the IBE bit to 1 to reflect the pin state in the corresponding GPDI register. Clear

the IBE to 0 to reduce power consumption. When configured as GPI, set the IBE bit to 1.

DSC ODE

3

3

When configured as DATA[0:31], clear the ODE bit to 0.

HYS

4

4

If external master operation is enabled, clear the HYS bit to 0.

00

WPE

5

5

Refer to the EBI section for weak pullup settings when configured as DATA[0:31].

WPS

5

W

RESET: 000000001100001 1

Loading...

Loading...