MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-67

12.4.2.12 Calibration Bus Operation — MPC5553 Only

The MPC5553 EBI has a second external bus, intended for calibration use. This bus consists of a second

set of the same signals present on the primary external bus (some are shared), except that arbitration, (and

optionally other signals also) are excluded. Both busses are supported by the EBI by using the calibration

chip selects to steer accesses to the calibration bus instead of to the primary external bus.

Because the calibration bus has no arbitration signals, the arbitration on the primary bus controls accesses

on the calibration bus as well, and no external master accesses can be performed on the calibration bus.

Accesses cannot be performed in parallel on both external busses. However, back-to-back accesses can

switch from one bus to the other, as determined by the type of chip select each address matches.

The timing diagrams and protocol for the calibration bus is identical to the primary bus, except that some

signals are missing on the calibration bus.

There is an inherent dead cycle between a calibration chip select access and a non-calibration access (chip

select or non-chip select), just like the one between accesses to two different non-calibration chip selects

(described in Section 12.4.2.4.3, “Back-to-Back Accesses”).

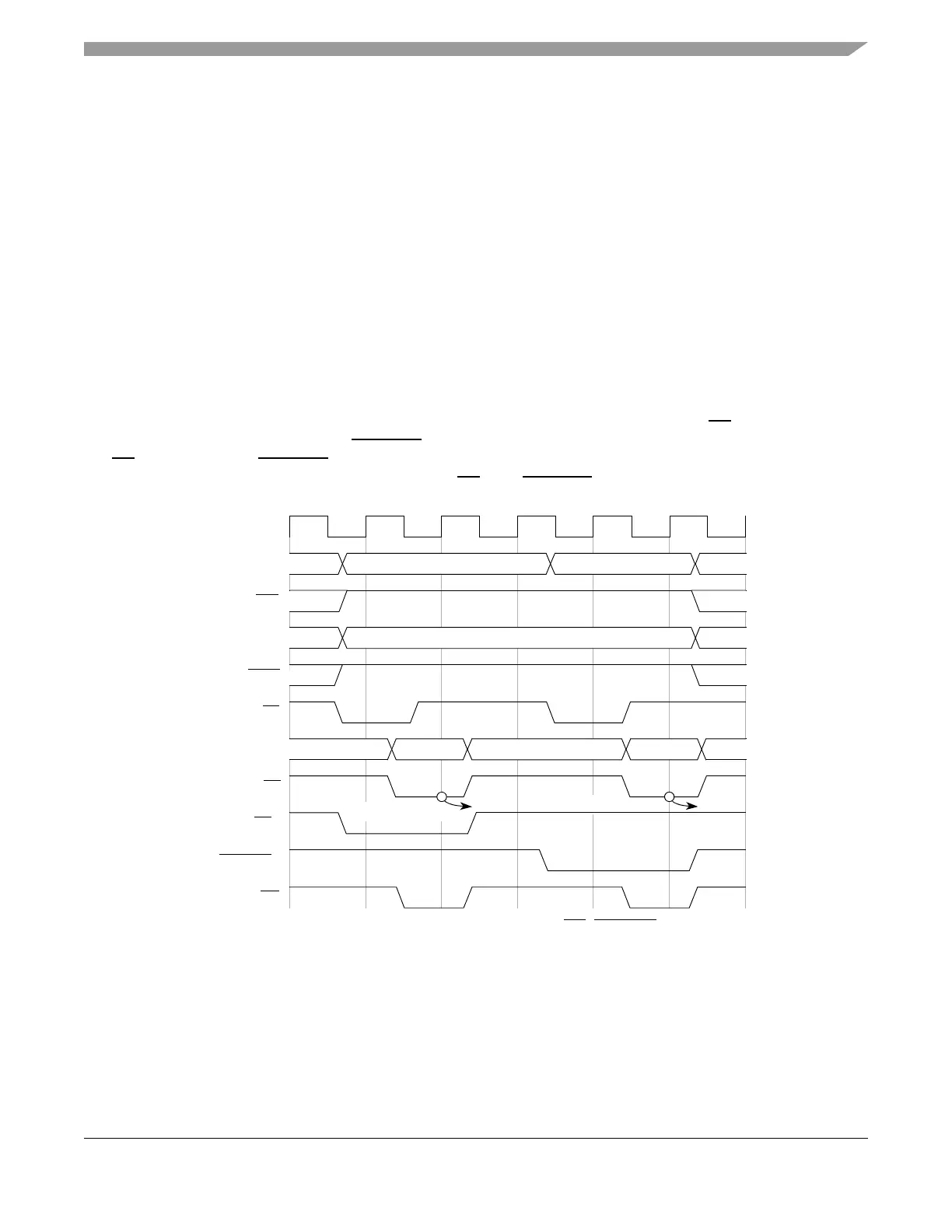

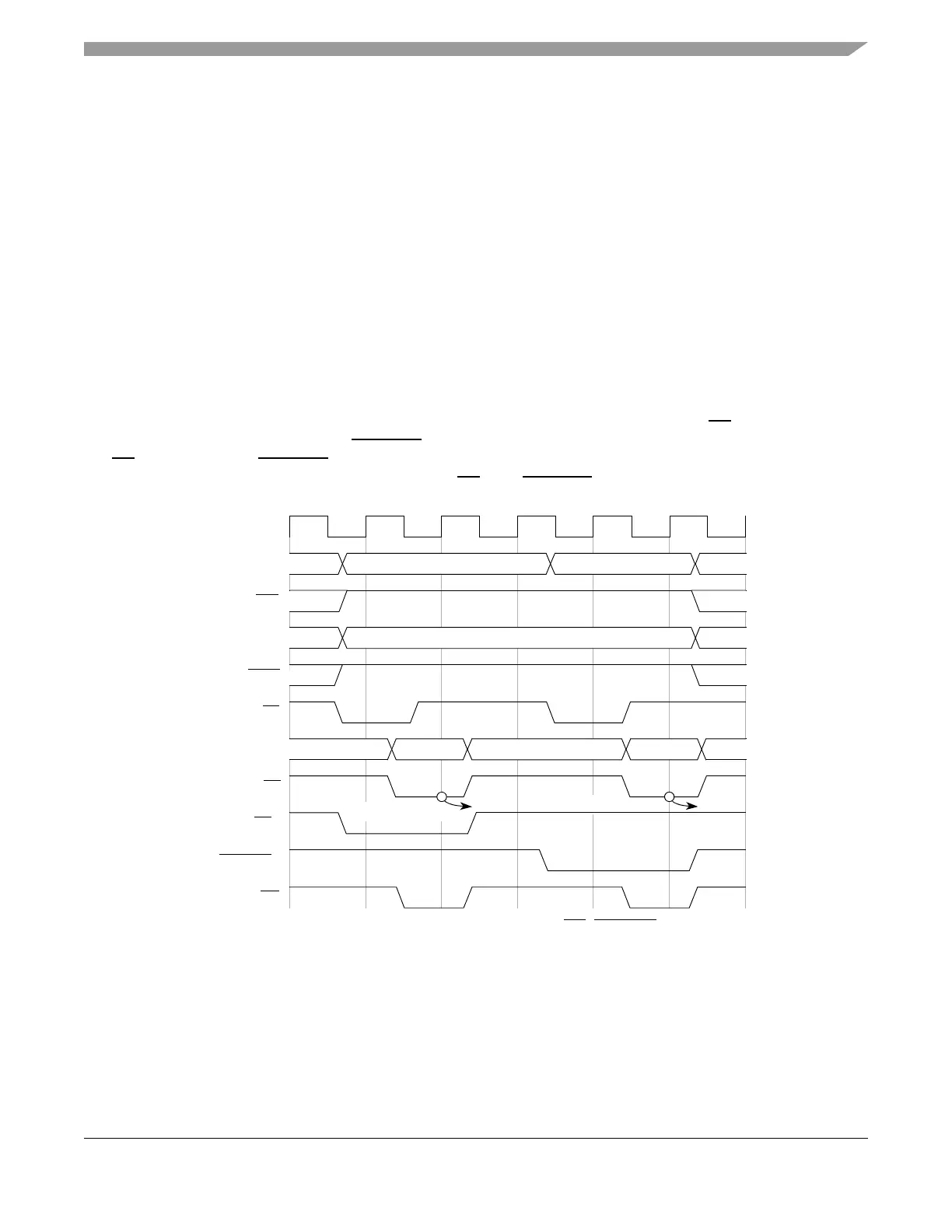

Figure 12-50 shows an example of a non-calibration chip select read access (CSx) followed by a

calibration chip select read access (CAL_CSy). Note that this figure is identical to Figure 12-18, except

the CSy is replaced by CAL_CSy. Timing for other cases on the calibration bus can similarly be derived

from other figures in this document (by replacing CS with CAL_CS).

Figure 12-50. Back-to-Back 32-bit Reads to CS, CAL_CS Banks

DATA is valid

CLKOUT

ADDR[8:31]

TS

DATA[0:31]

TA

RD_WR

TSIZ[0:1]

BDIP

OE

CAL_CSy

00

DATA is valid

CSx

Loading...

Loading...