MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-11

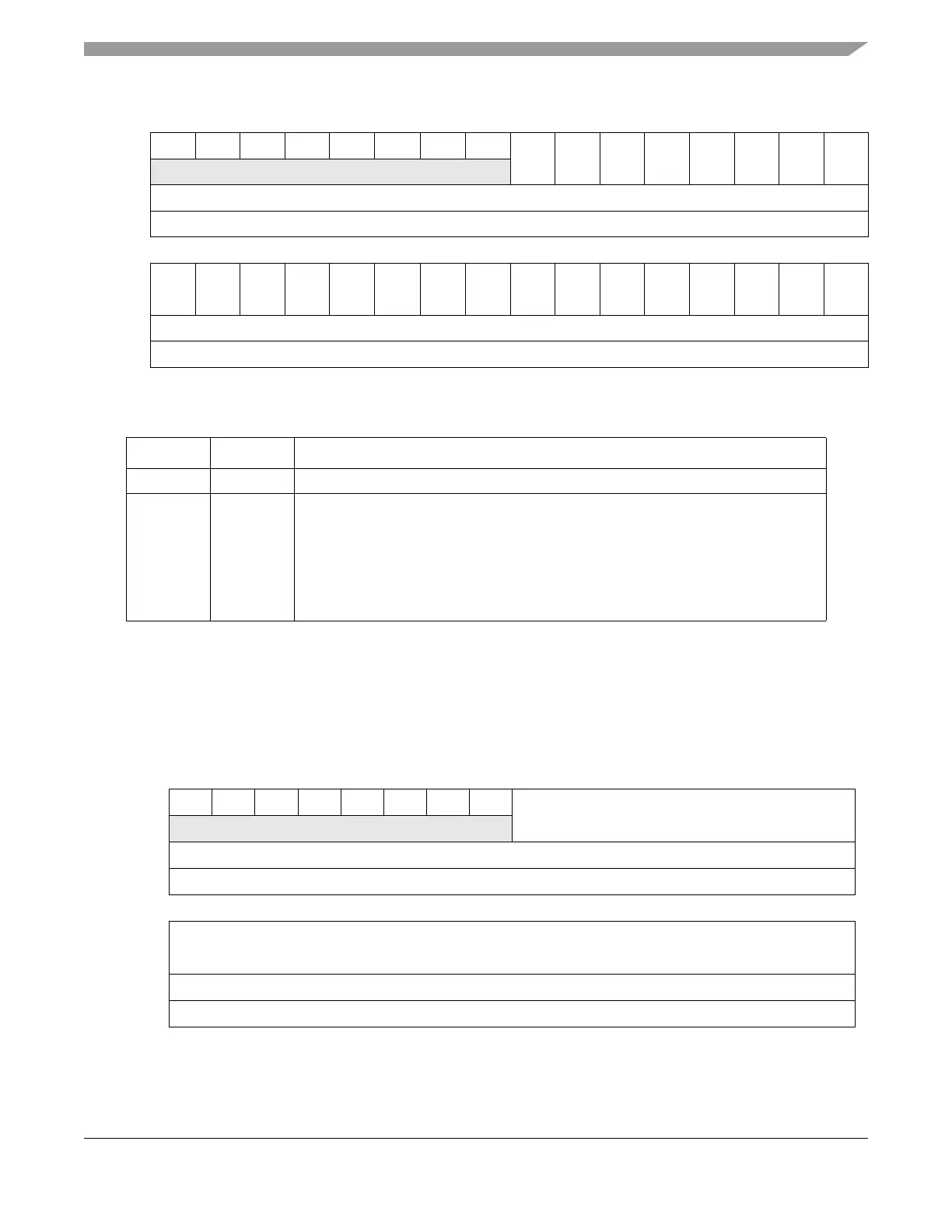

17.3.1.4 eMIOS Channel A Data Register (EMIOS_CADRn)

Depending on the mode of operation, internal registers A1 or A2, used for matches and captures, can be

assigned to address EMIOS_CADRn. Both A1 and A2 are cleared by reset. Table 17-9 summarizes the

EMIOS_CADRn writing and reading accesses for all operating modes. For more information see section

Section 17.4.4.4, “Modes of Operation of the Unified Channels.”

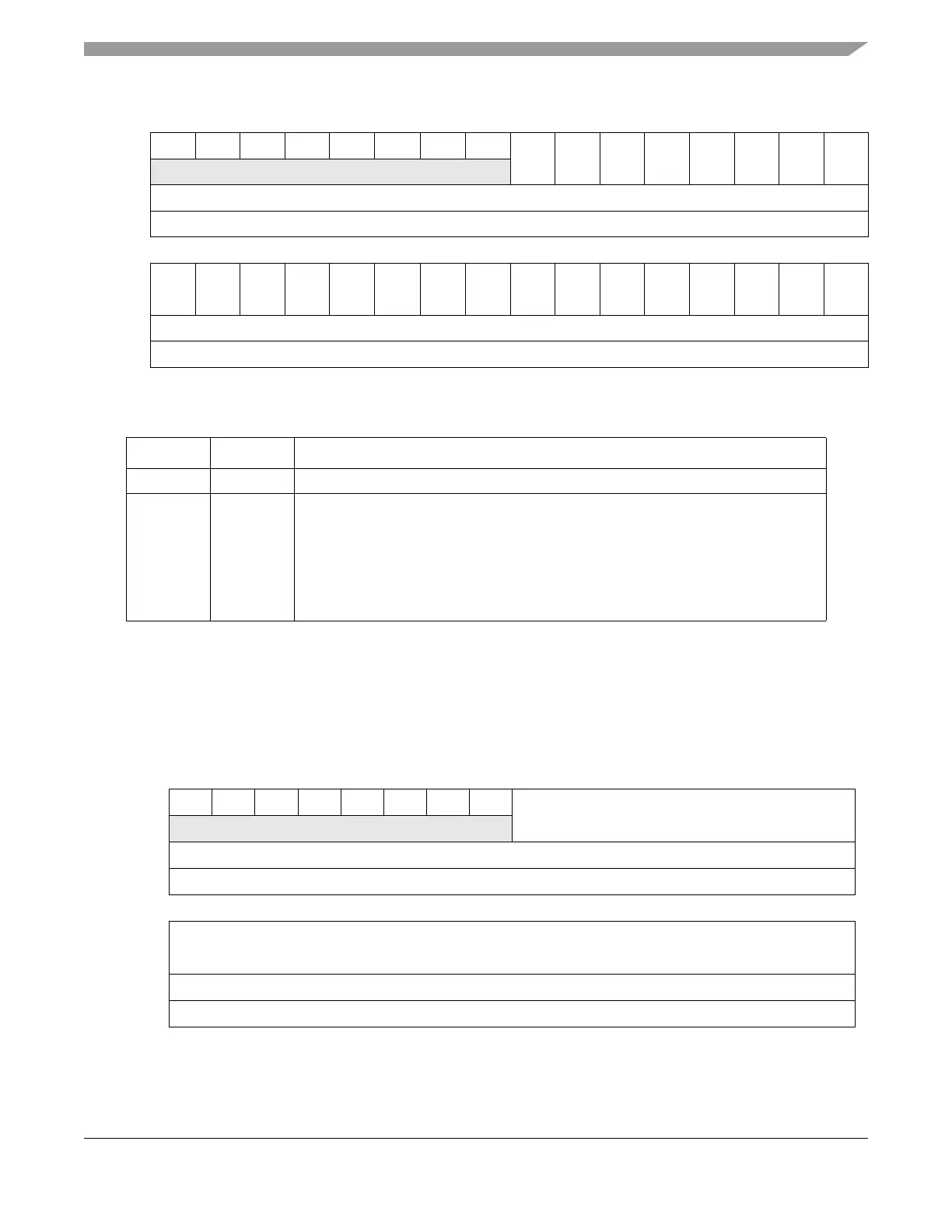

0123456789101112131415

R00000000OU23OU22OU21OU20OU19OU18OU17OU16

W

Reset0000000000000000

Reg Addr Base + 0x0008

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R OU15 OU14 OU13 OU12 OU11 OU10 OU9 OU8 OU7 OU6 OU5 OU4 OU3 OU2 OU1 OU0

W

Reset0000000000000000

Reg Addr Base + 0x0008

Figure 17-4. eMIOS Output Update Disable Register (EMIOS_OUDR)

Table 17-8. EMIOS_OUDR Field Descriptions

Bits Name Description

0–7 — Reserved.

8–31 OUn Channel n output update disable. When running in MC mode or an output mode,

values are written to registers A2 and B2. OUn bits are used to disable transfers from

registers A2 to A1 and B2 to B1. Each bit controls one channel.

0 Transfer enabled. Depending on the operating mode, transfer may occur

immediately or in the next period. Unless stated otherwise, transfer occurs

immediately.

1 Transfers disabled

0123456789101112131415

R00000000 A

W

Reset0000000000000000

Reg Addr UCn Base + 0x00

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RA

W

Reset0000000000000000

Reg Addr UCn Base + 0x00

Figure 17-5. eMIOS Channel A Data Register (EMIOS_CADRn)

Loading...

Loading...