MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

17-12 Freescale Semiconductor

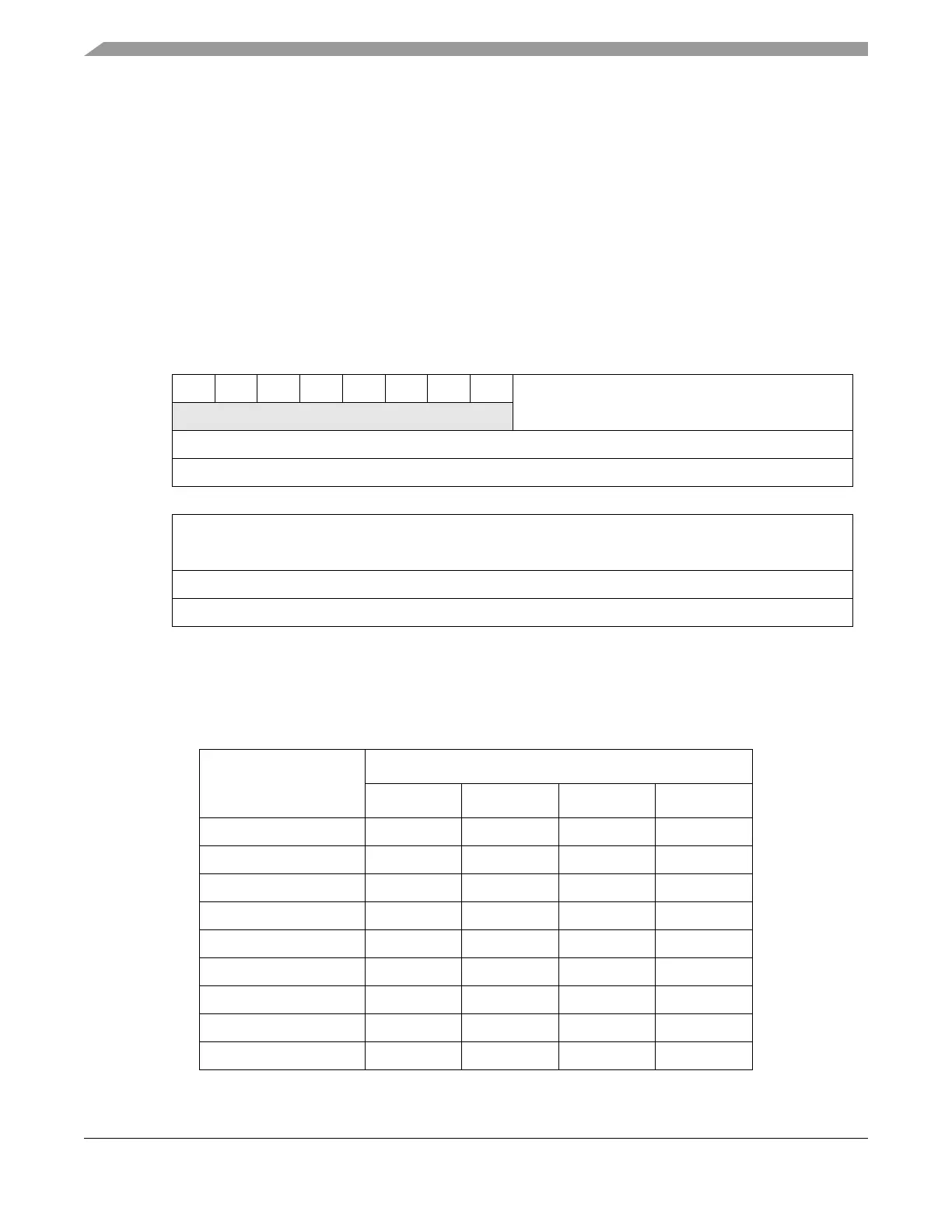

17.3.1.5 eMIOS Channel B Data Register (EMIOS_CBDRn)

Depending on the mode of operation, internal registers B1 or B2 can be assigned to address

EMIOS_CBDRn. Both B1 and B2 are cleared by reset. Table 17-9 summarizes the EMIOS_CBDRn

writing and reading accesses for all operating modes. For more information see section Section 17.4.4.4,

“Modes of Operation of the Unified Channels.”

NOTE

The EMIOS_CBDRn must not be read speculatively. For future

compatibility, the TLB entry covering the EMIOS_CBDRn must be

configured to be guarded.

0123456789101112131415

R00000000 B

W

Reset0000000000000000

Reg Addr UCn Base + 0x0004

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RB

W

Reset0000000000000000

Reg Addr UCn Base + 0x0004

Figure 17-6. eMIOS Channel B Data Register (EMIOS_CBDRn)

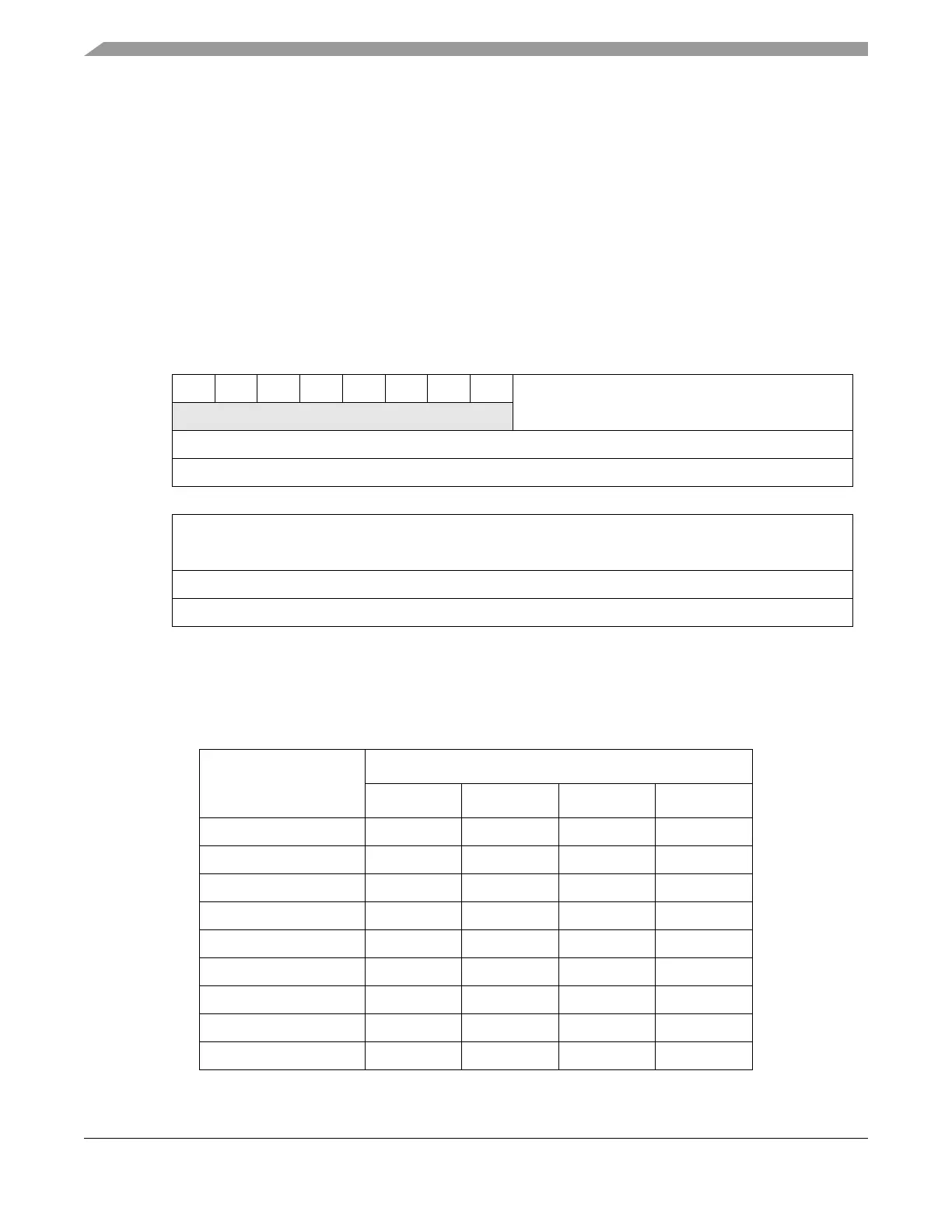

Table 17-9. EMIOS_CADRn and EMIOS_CBDRn Value Assignments

Operating Mode

Register Access

Write Read Write Read

GPIO A1, A2 A1 B1,B2 B1

SAIC

1

—A2B2B2

SAOC

1

A2 A1 B2 B2

IPWM — A2 — B1

IPM — A2 — B1

DAOC A2 A1 B2 B1

PEA A1 A2 — B1

PEC

1

A1 A1 B1 B1

QDEC

1

A1 A1 B2 B2

Loading...

Loading...