MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-85

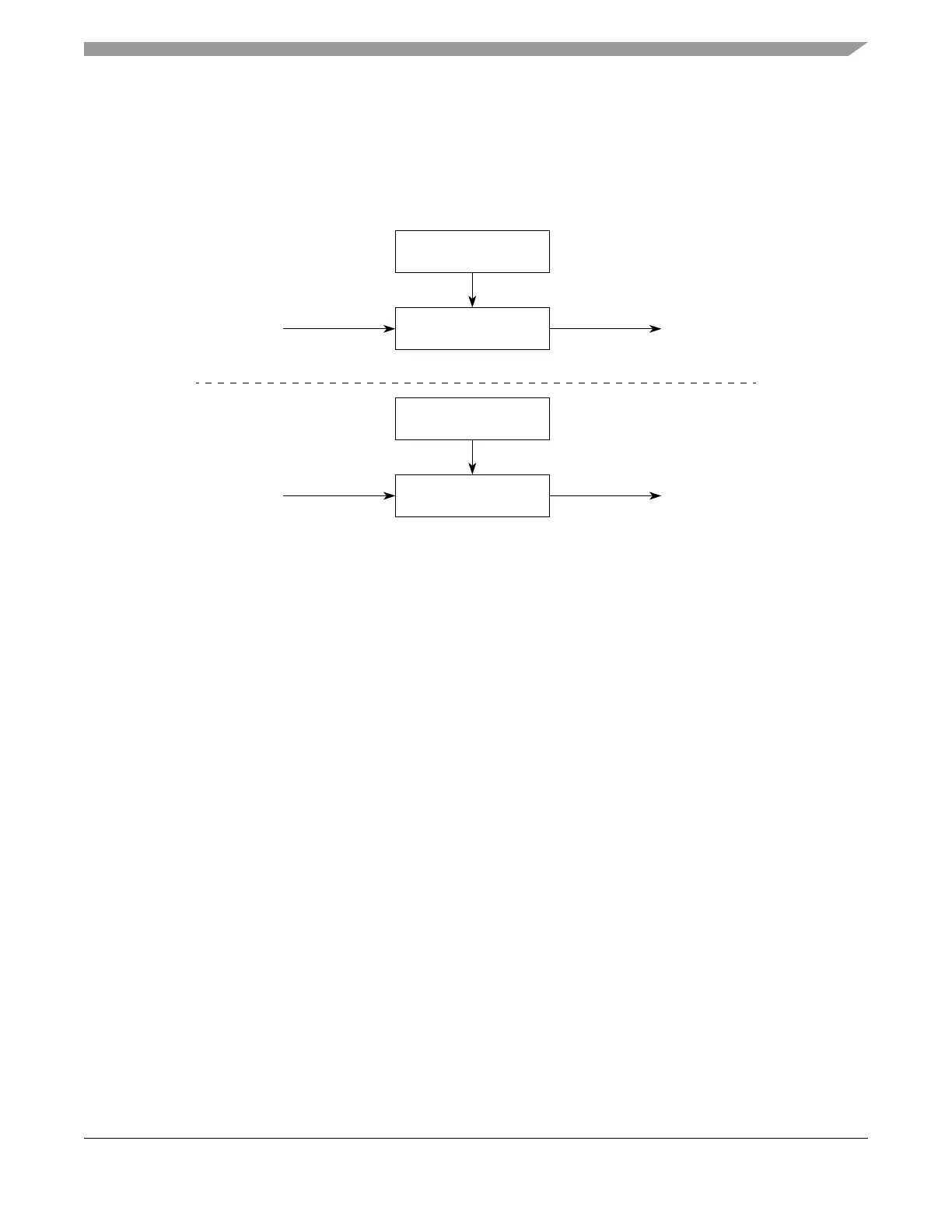

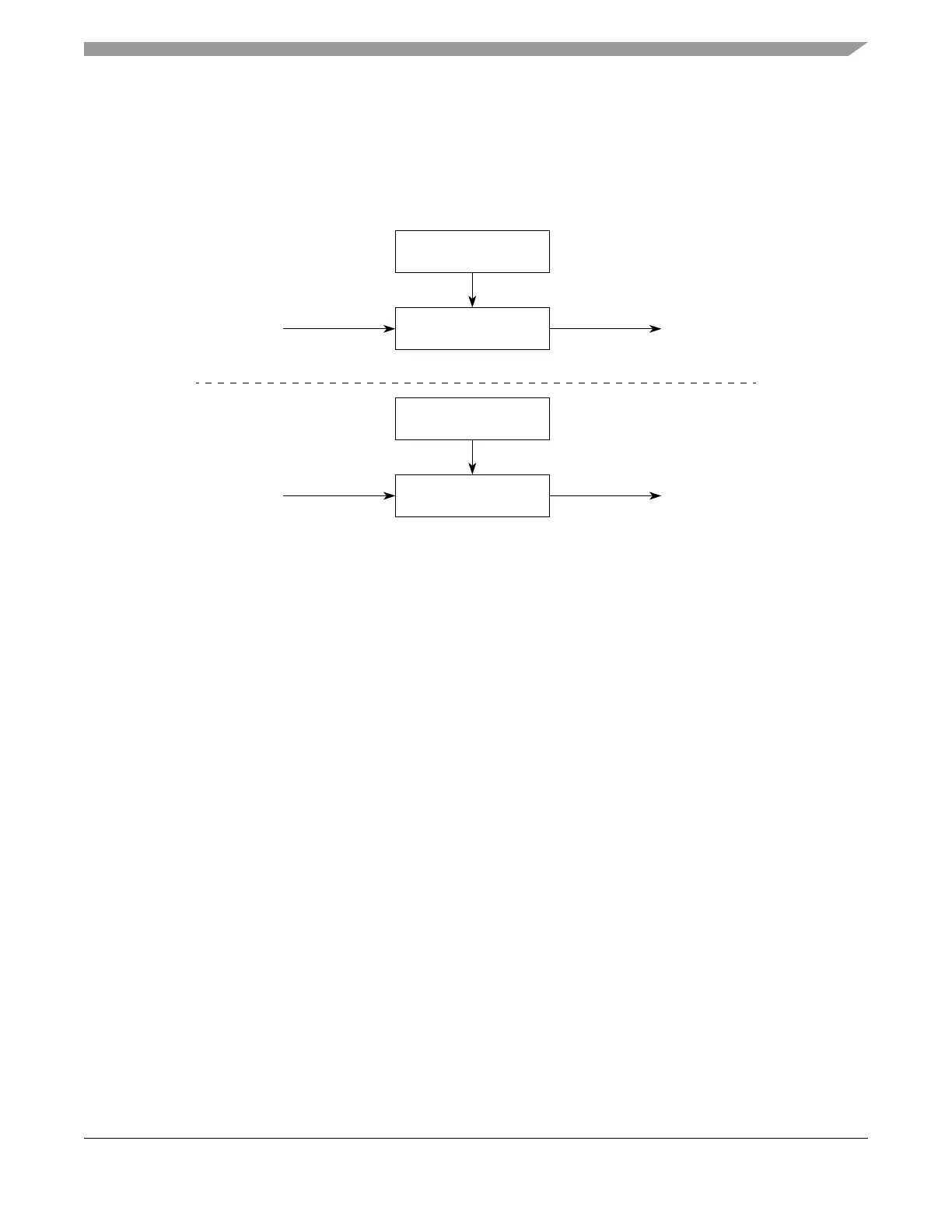

Figure 19-48 depicts how the ADC clocks for ADC0 and ADC1 are generated.

Figure 19-48. ADC0/1 Clock Generation

The ADC conversion speed (in kilosamples per second – ksamp/s)is calculated by the following formula.

The number of sampling cycles is determined by the LST bits in the command message — see Section ,

“ Conversion Command Message Format for On-Chip ADC Operation,” — and it can take one of the

following values: 2, 8, 64, or 128 ADC clock cycles. The number of AD conversion cycles is 13 for

differential conversions and 14 for single-ended conversions. The maximum conversion speed is achieved

when the ADC Clock frequency is set to its maximum (12Mhz) and the number of sampling cycles set to

its minimum (2 cycles). The maximum conversion speed for differential and single-ended conversions are

800ksamp/s and 750ksamp/s, respectively.

Table 19-47 shows an example of how the ADC0/1_CLK_PS can be set when using a 120 MHz system

clock and the corresponding conversion speeds for all possible ADC clock frequencies. The table also

shows that according to the system clock frequency, certain clock divide factors are invalid (2, 4, 6, 8 clock

divide factors in the example) because their use would result in a ADC clock frequency higher than the

maximum one supported by the ADC. ADC clock frequency must not exceed 12 Mhz.

ADCClockFrequency

SystemClockFrequency MHz

SystemClockDivideFactor

---------------------------------------------------------------------------------------- ADCClockFrequency 12MHz;=

Divide by:

2, 4, 6, ..., 60, 62, 64

ADC0

Control Register

To ADC0

ADC0_CLK_PS

ADC0 Clock

System

Clock

System Clock Divider

Divide by:

2, 4, 6, ..., 60, 62, 64

ADC1

Control Register

To ADC1

ADC1_CLK_PS

ADC1 Clock

System

Clock

System Clock Divider

ADCConversionSpeed

ADCClockFrequency MHz

NumberOfSamplingCycles NumberOfADConversionCycles+

--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------=

Loading...

Loading...