MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-97

Table 19-55 describes a list of methods to generate eDMA requests by the eQADC.

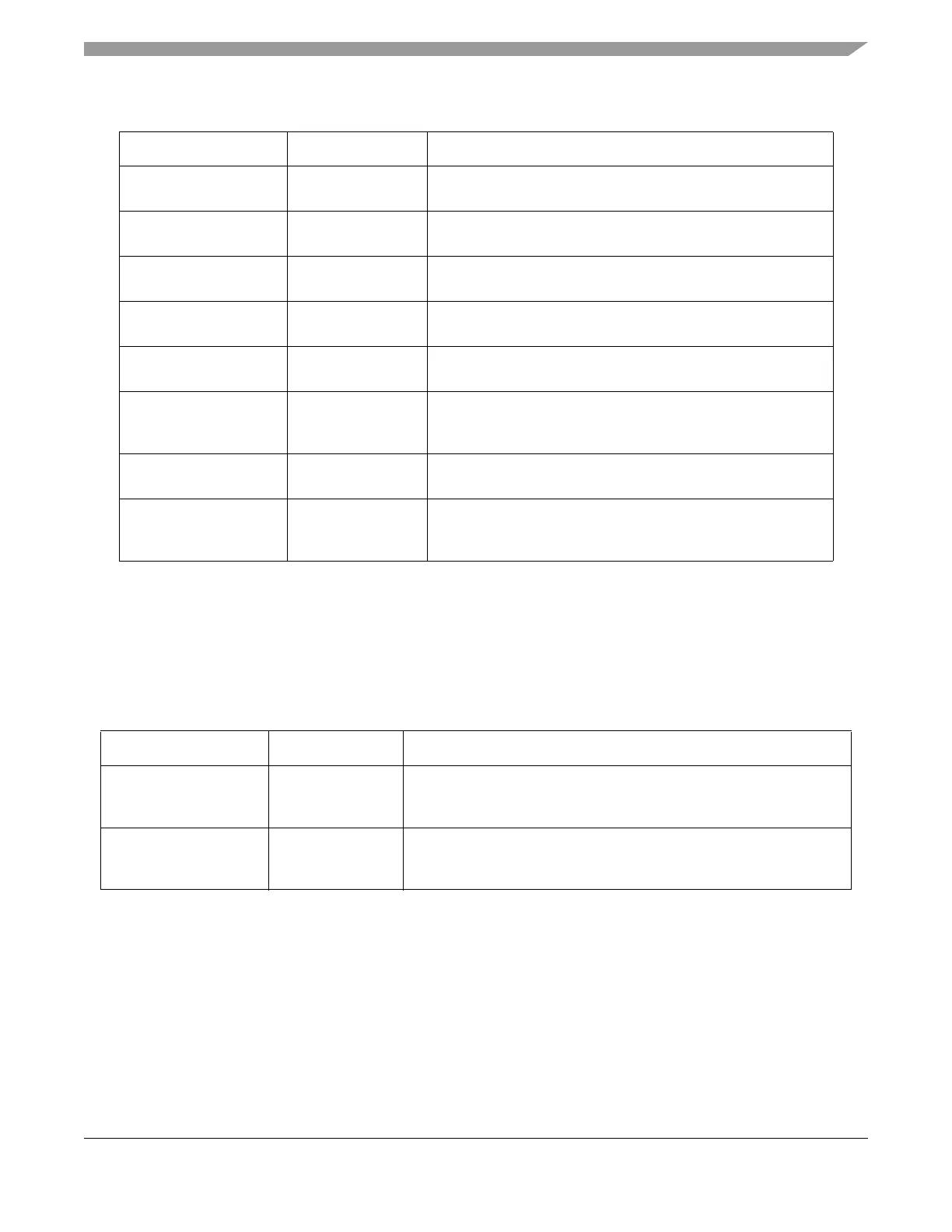

Table 19-54. eQADC FIFO Interrupt Summary

1

1

For details refer to Section 19.3.2.8, “eQADC FIFO and Interrupt Status Registers 0–5 (EQADC_FISRn),” and

Section 19.3.2.7, “eQADC Interrupt and eDMA Control Registers 0–5 (EQADC_IDCRn).”

Interrupt Condition Clearing Mechanism

Non Coherency Interrupt NCIEn = 1

NCFn = 1

Clear NCFn bit by writing a 1 to the bit.

Trigger Overrun Interrupt

2

TORIEn = 1

TORFn =1

Clear TORFn bit by writing a 1 to the bit.

Pause Interrupt PIEn = 1

PFn =1

Clear PFn bit by writing a 1 to the bit.

End of Queue Interrupt EOQIEn = 1

EOQFn = 1

Clear EOQFn bit by writing a 1 to the bit.

Command FIFO

Underflow Interrupt

2

CFUIEn = 1

CFUFn = 1

Clear CFUFn bit by writing a 1 to the bit.

Command FIFO

Fill Interrupt

CFFEn = 1

CFFSn = 0

CFFFn = 1

Clear CFFFn bit by writing a 1 to the bit.

Result FIFO Overflow

Interrupt

2

2

Apart from generating an independent interrupt request for when a RFIFO overflow interrupt, a CFIFO underflow

interrupt, and a CFIFO trigger overrun interrupt occurs, the eQADC also provides a combined interrupt request at

which these requests from ALL CFIFOs are ORed. Refer to Figure 19-54 for details.

RFOIEn = 1

RFOFn = 1

Clear RFOFn bit by writing a 1 to the bit.

Result FIFO

Drain Interrupt

RFDEn = 1

RFDSn = 0

RFDFn = 1

Clear RFDFn bit by writing a 1 to the bit.

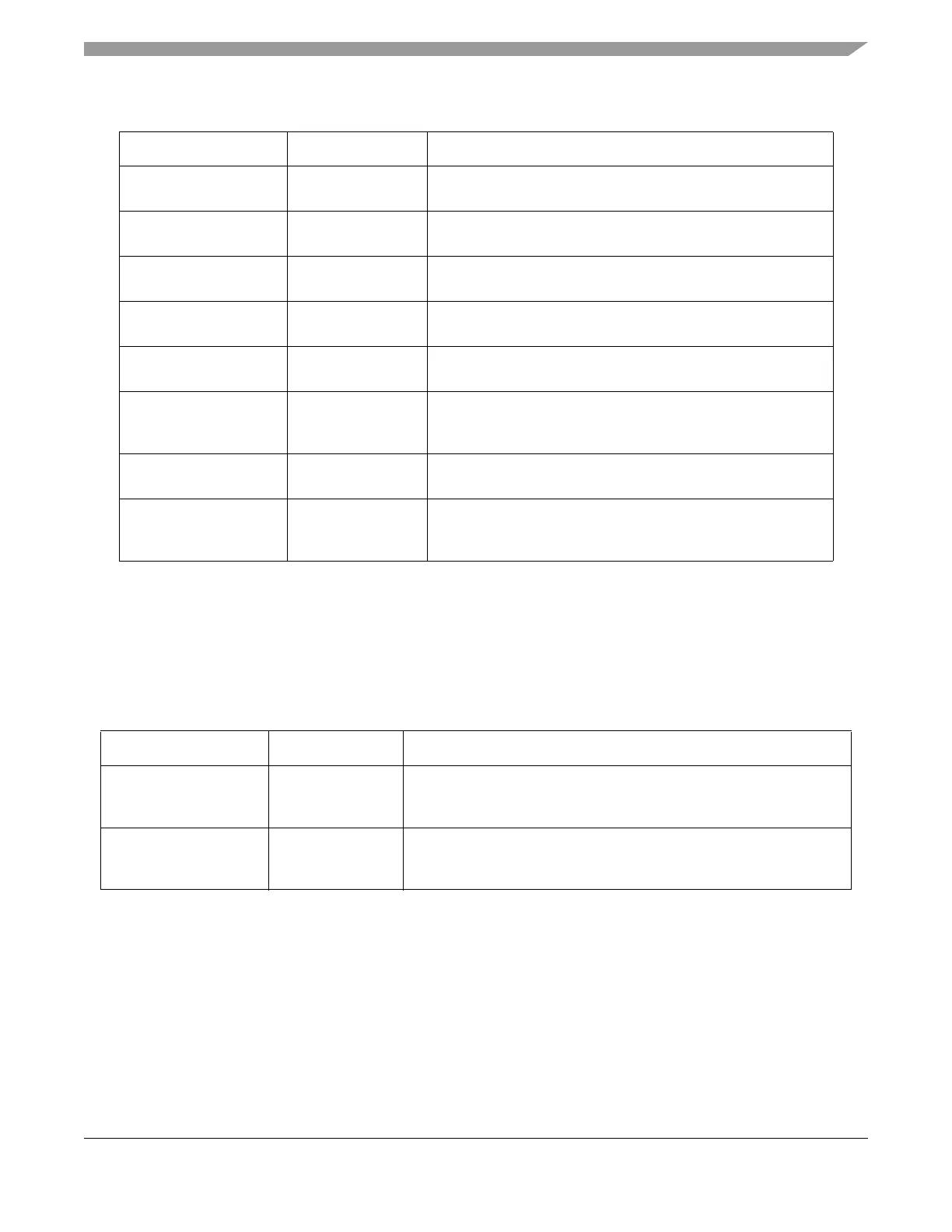

Table 19-55. eQADC FIFO eDMA Summary

1

1

For details refer to Section 19.3.2.8, “eQADC FIFO and Interrupt Status Registers 0–5 (EQADC_FISRn),” and

Section 19.3.2.7, “eQADC Interrupt and eDMA Control Registers 0–5 (EQADC_IDCRn).”

eDMA Request Condition Clearing Mechanism

Result FIFO Drain

eDMA Request

RFDEn = 1

RFDSn = 1

RFDFn = 1

The eQADC automatically clears the RFDFn when RFIFOn becomes

empty. Writing 1 to the RFDFn bit is not allowed while RDFS = 1.

Command FIFO Fill

eDMA Request

CFFEn = 1

CFFSn = 1

CFFFn = 1

The eQADC automatically clears the CFFFn when CFIFOn becomes

full. Writing 1 to the CFFFn bit is not allowed while CFDS = 1.

Loading...

Loading...