MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-15

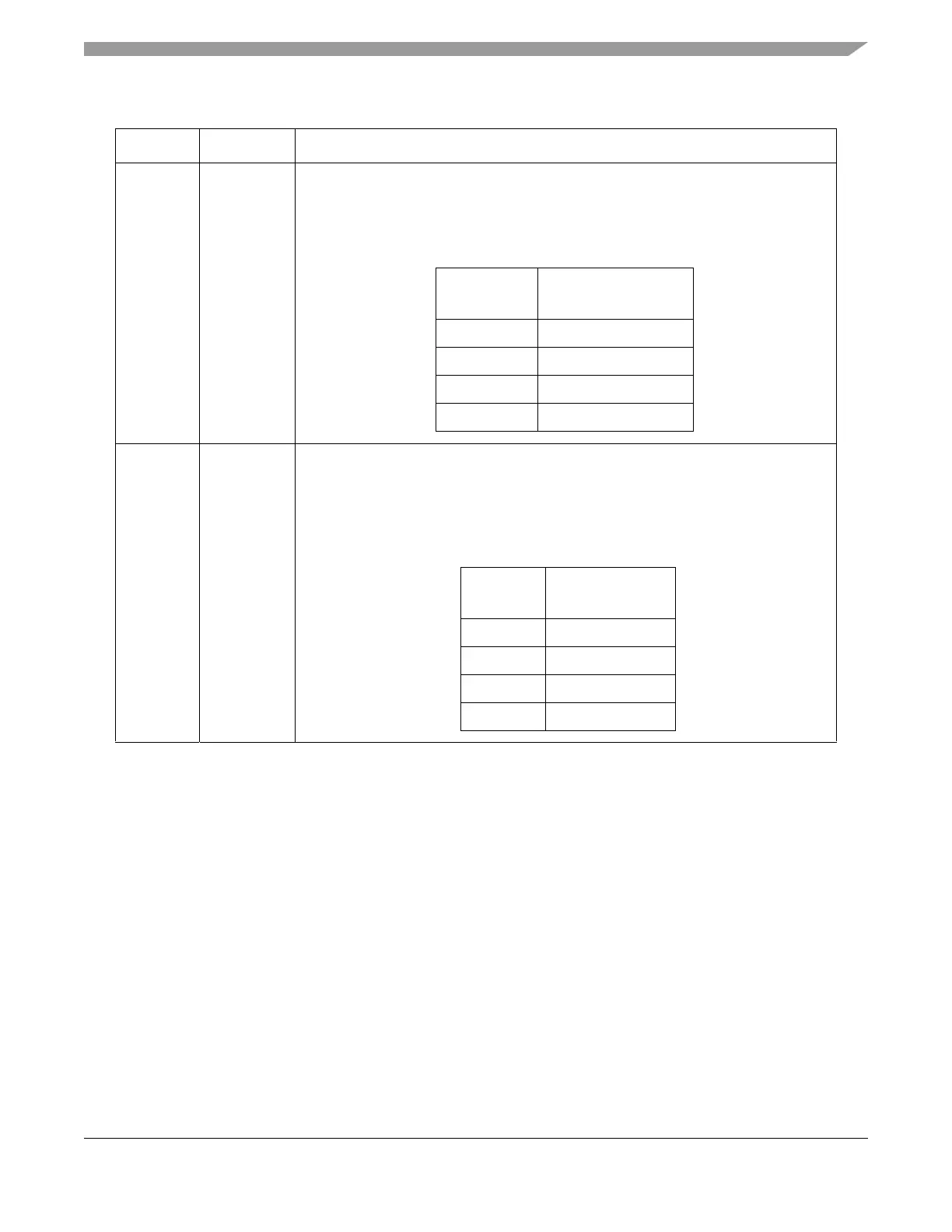

12–13 PDT

[0:1]

Delay after transfer prescaler. The PDT field selects the prescaler value for the delay

between the negation of the PCS signal at the end of a frame and the assertion of PCS

at the beginning of the next frame. The PDT field is only used in master mode. The table

below lists the prescaler values. The description for bitfield DT in Tabl e 20 -5 details how

to compute the delay after transfer.

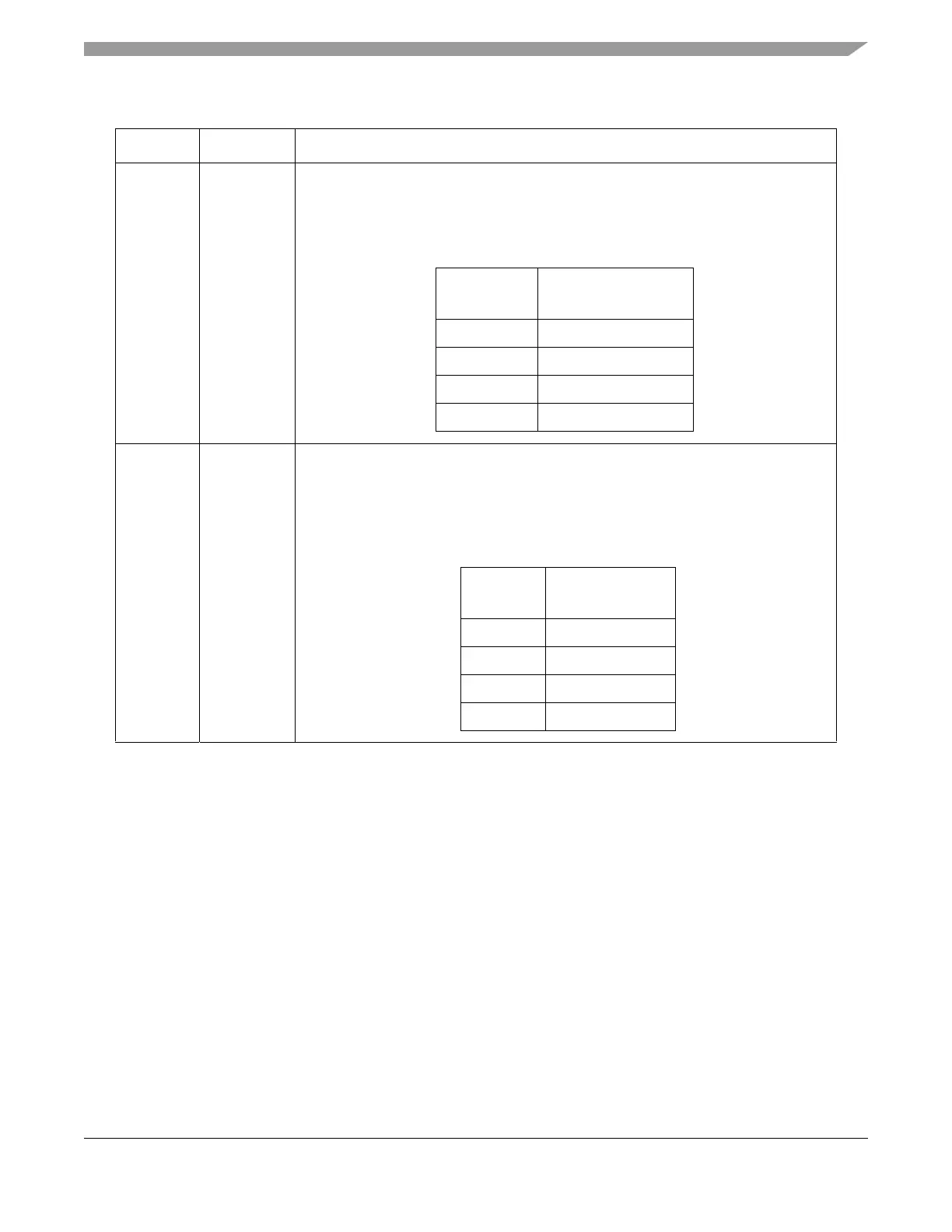

14–15 PBR

[0:1]

Baud rate prescaler. Selects the prescaler value for the baud rate. This field is only used

in master mode. The baud rate is the frequency of the serial communications clock

(SCK). The system clock is divided by the prescaler value before the baud rate selection

takes place. The baud rate prescaler values are listed in the table below. The

description for Section 20.4.6.1, “Baud Rate Generator” details how to compute the

baud rate.

Table 20-5. DSPIx_CTARn Field Description (Continued)

Bits Name Description

PDT

Delay after Transfer

Prescaler Value

00 1

01 3

10 5

11 7

PBR

Baud Rate

Prescaler Value

00 2

01 3

10 5

11 7

Loading...

Loading...