GD32F3x0 User Manual

205

whitchmake the CMP exit from power saving modes.

13.3.3. CMP operating mode

For a given application, there is a trade-off between the CMP power consumption versus

propagation delay, which is adjusted by configuring bits CMPxM [1:0] in CMP_CS register.

The CMP works fastest with highest power consumption when CMPxM = 2’b00, while works

slowest with lowest power consumption when CMPxM = 2’b11.

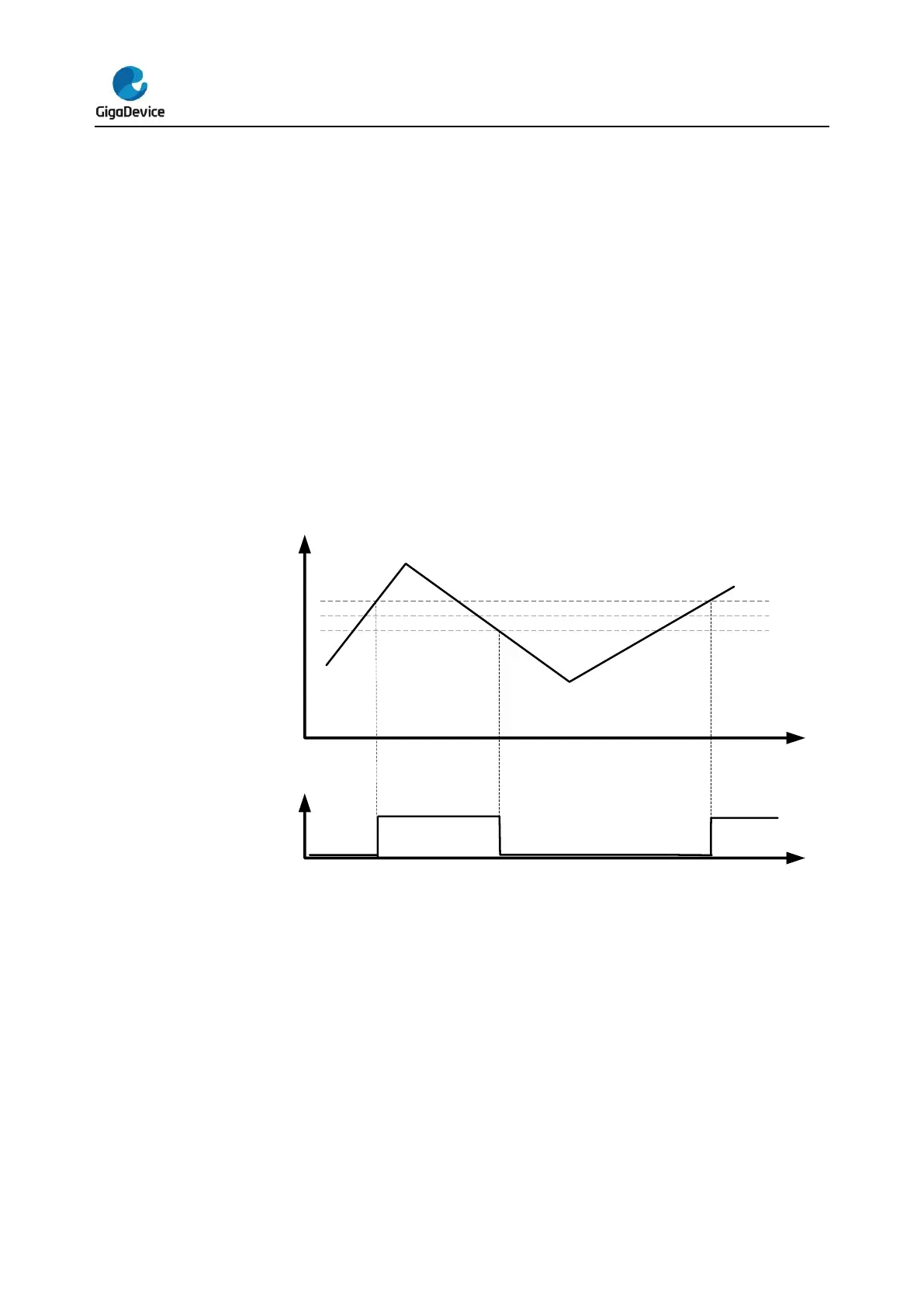

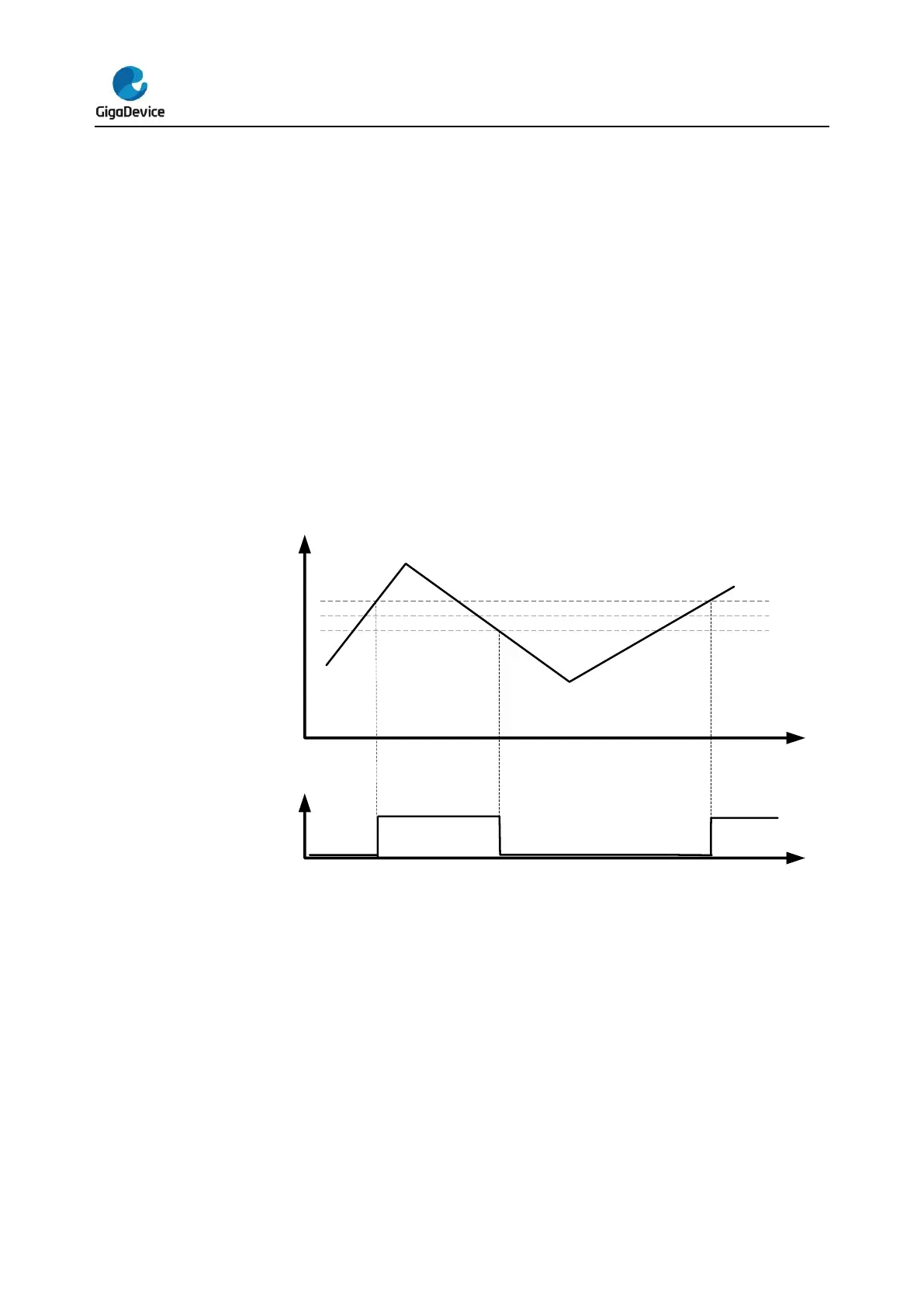

13.3.4. CMP hysteresis

In order to avoid spurious output transitions that caused by the noise signal, a programmable

hysteresis is designed to force the hysteresis value using external components. This function

can be shut down when you don't need it.

Figure 13-2. CMP hysteresis

13.3.5. CMP register write protection

The CMP control and status register (CMP_CS) can be protected from writing by setting

CMPxLK bit to 1. The CMP_CS register, including the CMPxLK bit will be read-only, and can

only be reset by the MCU reset.

Loading...

Loading...