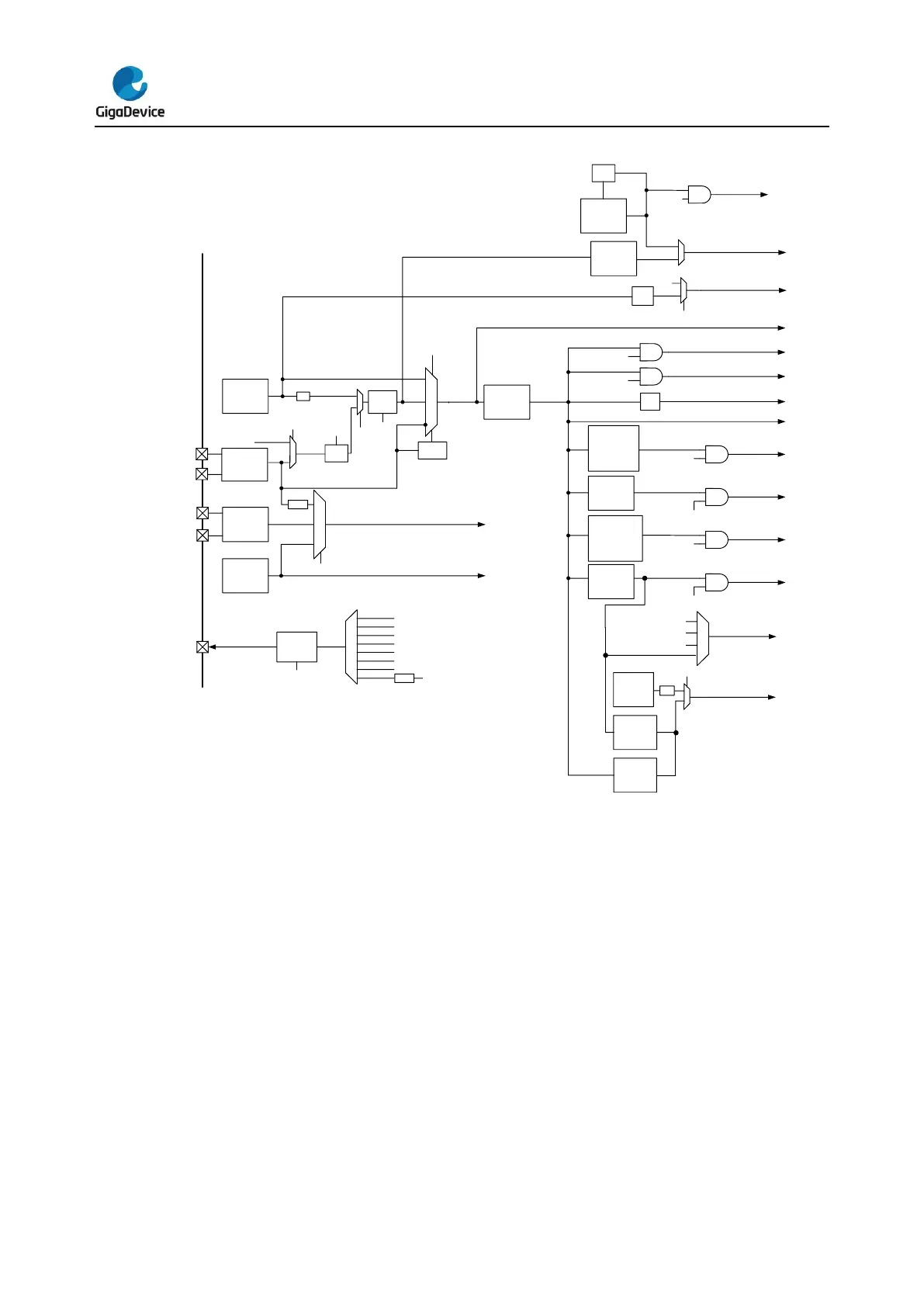

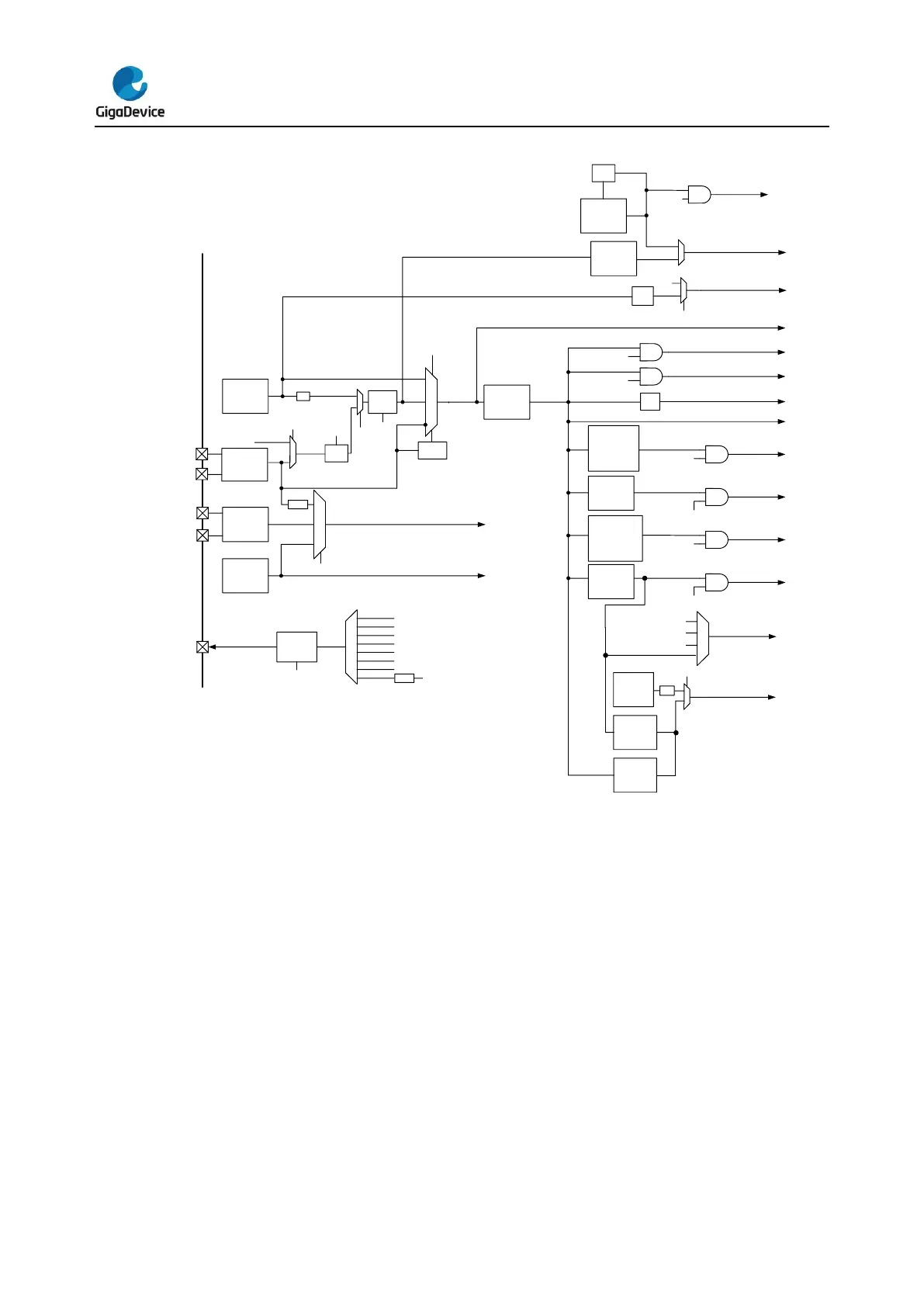

The frequency of AHB, APB2 and the APB1 domains can be configured by each prescaler.

The maximum frequency of the AHB, APB2 and APB1 domains is 108 MHz/54 MHz/54 MHz.

The cortex system timer (systick) external clock is clocked with the AHB clock (HCLK)

divided by 8. The systick can work either with this clock or with the AHB clock (HCLK),

configurable in the systick control and status register.

The ADC are clocked by the clock of APB2 divided by 2, 4, 6, 8 or by the clock of AHB

divided by 3, 5, 7, 9 or IRC28M or IRC28M/2 clock for GD32F3x0 series selected by

ADCSEL bit in configuration register 2 (RCU_CFG2). The USART0 is clocked by IRC8M

clock or LXTAL clock or system clock or APB2 clock, which selected by USART0SEL bits in

configuration register 2 (RCU_CFG2). The CEC clock is clocked by IRC8M divided 244 or

LXTAL clock which selected by CECSEL bit in configuration register 2 (RCU_CFG2).

The RTC is clocked by LXTAL clock or IRC40K clock or HXTAL clock divided by 32 which

select by RTCSRC bit in backup domain control register (RCU_BDCTL).

The USBFS is clocked by the clock of CK48M. The CK48M is selected from the clock of

Loading...

Loading...