Alarm-0 function enable

0: Disable alarm function

1: Enable alarm function

Must be kept at reset value.

Clock System

0: 24-hour format

1: 12-hour format

Note: Can only be written in initialization state

Shadow registers bypass control

0: Reading calendar from shadow registers

1: Reading calendar from current real-time calendar

Note: If frequency of APB1 clock is less than seven times the frequency of

RTCCLK, this bit must set to 1.

Reference clock detection function enable

0: Disable reference clock detection function

1: Enable reference clock detection function

Note: Can only be written in initialization state and FACTOR_S must be 0x00FF

Valid event edge of time-stamp

0: rising edge is valid event edge for time-stamp event

1: falling edge is valid event edge for time-stamp event

Must be kept at reset value.

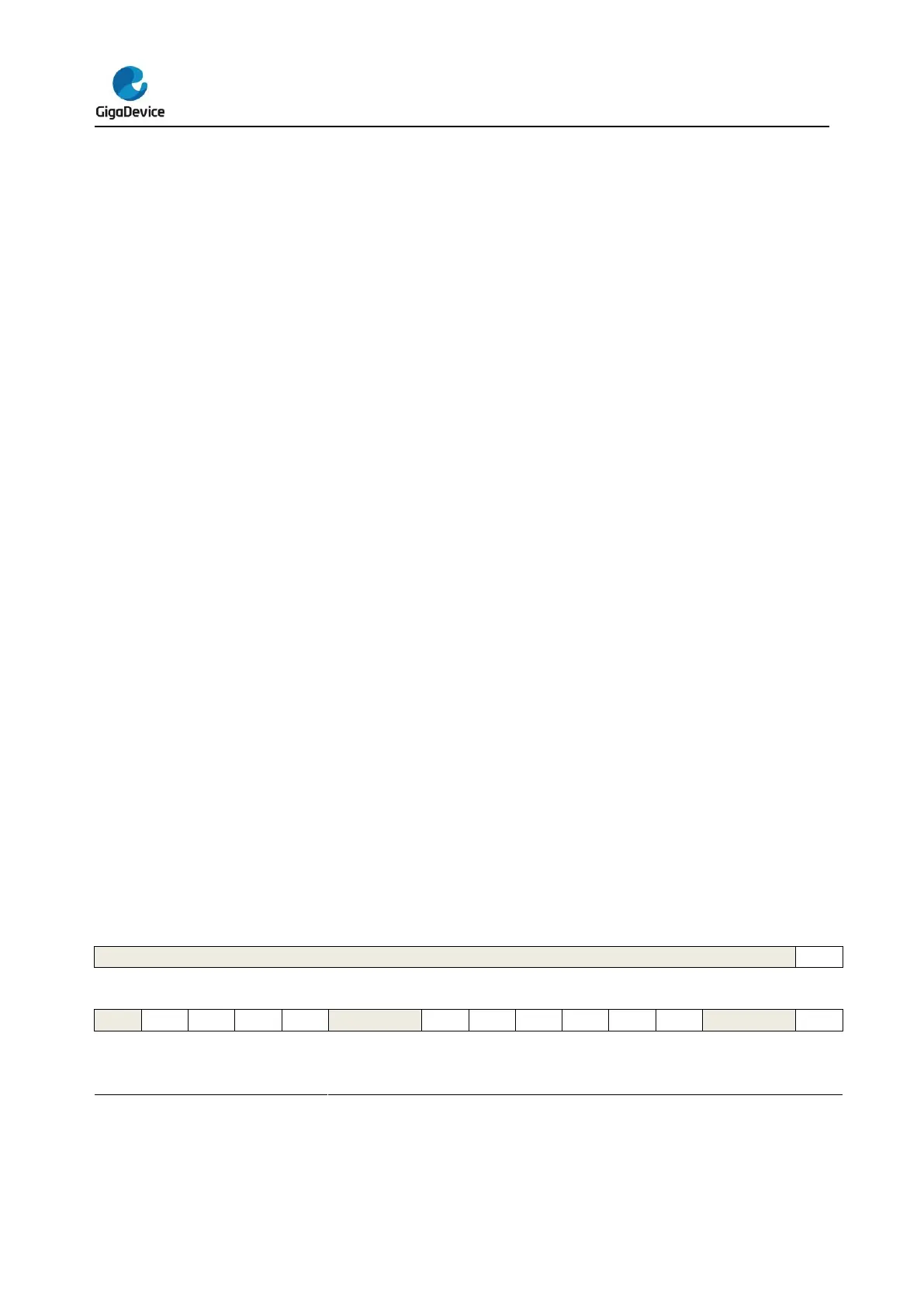

15.4.4. Status register (RTC_STAT)

Address offset: 0x0C

System reset: Only INITM, INITF and RSYNF bits are set to 0. Others are not affected.

Backup domain reset value: 0x0000 0007

This register is writing protected except RTC_STAT[14:8].

This register has to be accessed by word (32-bit).

Must be kept at reset value.

Smooth calibration pending flag

Set to 1 by hardware when software writes to RTC_HRFC without entering

Loading...

Loading...