This means that there is an opportunity for other devices to gain access to the CEC line

during the periods mentioned above to send their own messages after the current device has

finished sending its current message.

If SFT is not 0x0, the corresponding user configure SFT will be performed.

21.3.5. SFT option bit description

SFT option bit support another way for saving bus inactive time through setting more SFT

counter’s start time point.

When SFTOPT = 0, the SFT timer will start at the time STAOM bit asserted when the

controller is in the idle state.

When SFTOPT = 1, the SFT timer will start at the time CEC bus is in idle state and the SFT

time will be saved if you configure the STAOM after SFT done because the controller will

start transmit without any latency.

When SFTOPT = 1, some other cases will also start the SFT counter:

In case of regular TX/RX complete(TEND/REND asserted)

In case of transmission not complete such as the time TERR, TAERR or TU asserted.

In case of receiving progress, if some error detected and error bit is generated, the SFT

timer will start when output error bit finished.

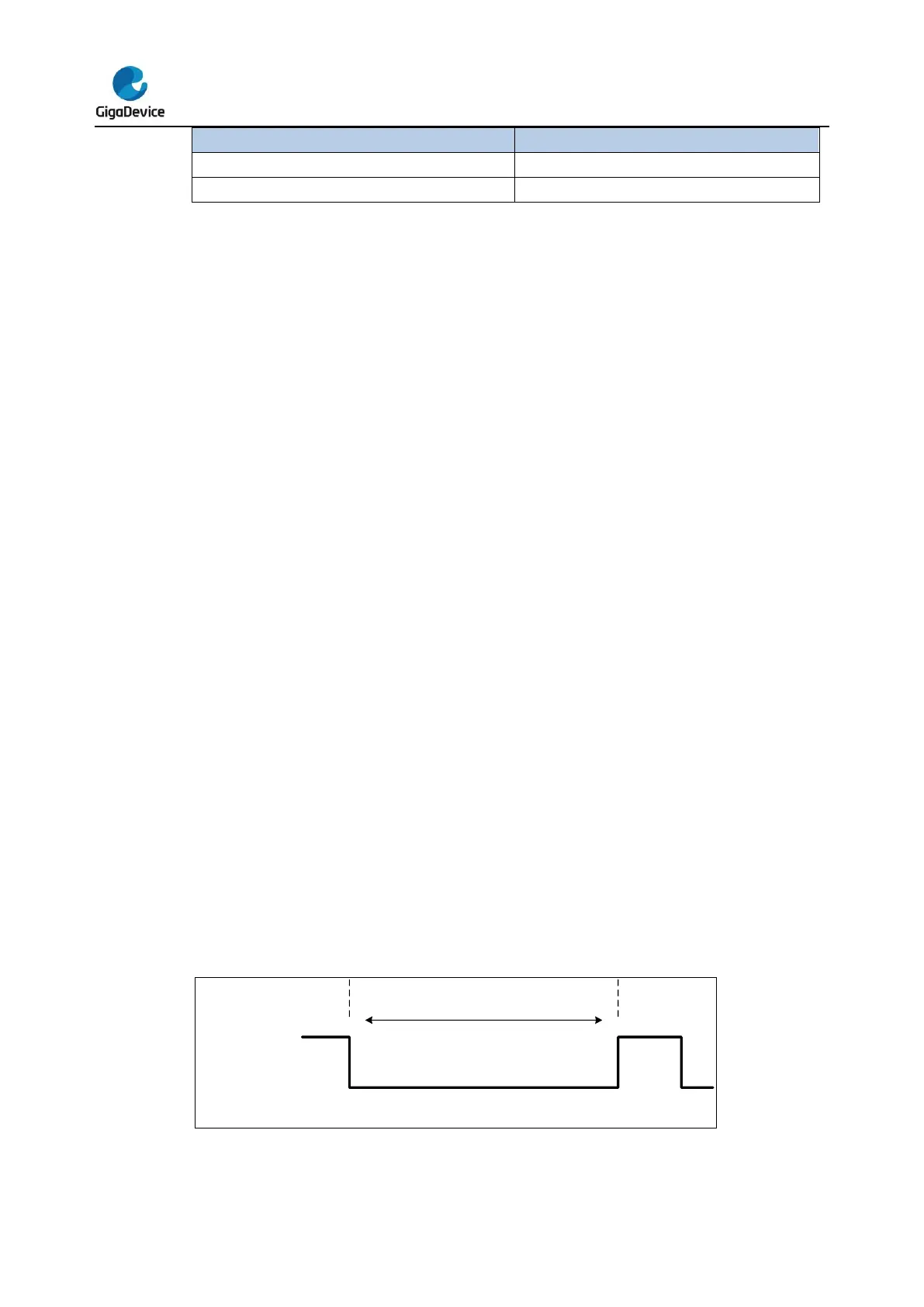

21.3.6. Error definition

Error-Bit

If some errors are occurred and corresponding generation configure is enabled the

HDMI-CEC controller will generate an error bit on the CEC pin for indicating. Error bit period

definition is shown as below:

Figure 21-5. Error Bit Period

Loading...

Loading...