GD32F3x0 User Manual

63

LDEN to 00 in the PMU_CTL register, and not in low-power mode depending on the LDOLP

bit reset in the PMU_CTL register.

Normal-driver/Low-power: The Deep-sleep mode is not in low-driver mode by configure

LDEN to 00 in the PMU_CTL register. The low-power mode enters depending on the LDOLP

bit set in the PMU_CTL register.

Low-driver/Normal-power: The low-driver mode in Deep-sleep mode when the LDO in

normal-power mode depending on the LDOLP bit reset in the PMU_CTL register enters by

configure LDEN to 0b11 and LDNP to 1 in the PMU_CTL register.

Low-driver/Low-power: The low-driver mode in Deep-sleep mode when the LDO in

low-power mode depending on the LDOLP bit set in the PMU_CTL register enters by

configure LDEN to 0b11 and LDLP to 1 in the PMU_CTL register.

No Low-driver: The Deep-sleep mode is not in low-driver mode by configure LDEN to 00 in

the PMU_CTL register.

Note: In order to enter Deep-sleep mode smoothly, all EXTI line pending status (in the

EXTI_PD register) and related peripheral flags must be reset, refer to Table 6-3. EXTI

source. If not, the program will skip the entry process of Deep-sleep mode to continue to

execute the following procedure.

Standby mode

The Standby mode is based on the SLEEPDEEP mode of the Cortex

®

-M4, too. In Standby

mode, the whole 1.2V domain is power off, the LDO is shut down, and all of IRC8M, IRC28M,

IRC48M, HXTAL and PLL are disabled. Before entering the Standby mode, it is necessary to

set the SLEEPDEEP bit in the Cortex

®

-M4 System Control Register, and set the STBMOD bit

in the PMU_CTL register, and clear WUF bit in the PMU_CS register. Then, the device

enters the Standby mode after a WFI or WFE instruction is executed, and the STBF status

flag in the PMU_CS register indicates that the MCU has been in Standby mode. There are

four wakeup sources for the Standby mode, including the external reset from NRST pin, the

RTC alarm/time stamp/tamper events, the FWDGT reset, and the rising edge on WKUP pins.

The Standby mode achieves the lowest power consumption, but spends longest time to

wake up. Besides, the contents of SRAM and registers in 1.2V power domain are lost in

Standby mode. When exiting from the Standby mode, a power-on reset occurs and the

Cortex

®

-M4 will execute instruction code from the 0x00000000 address.

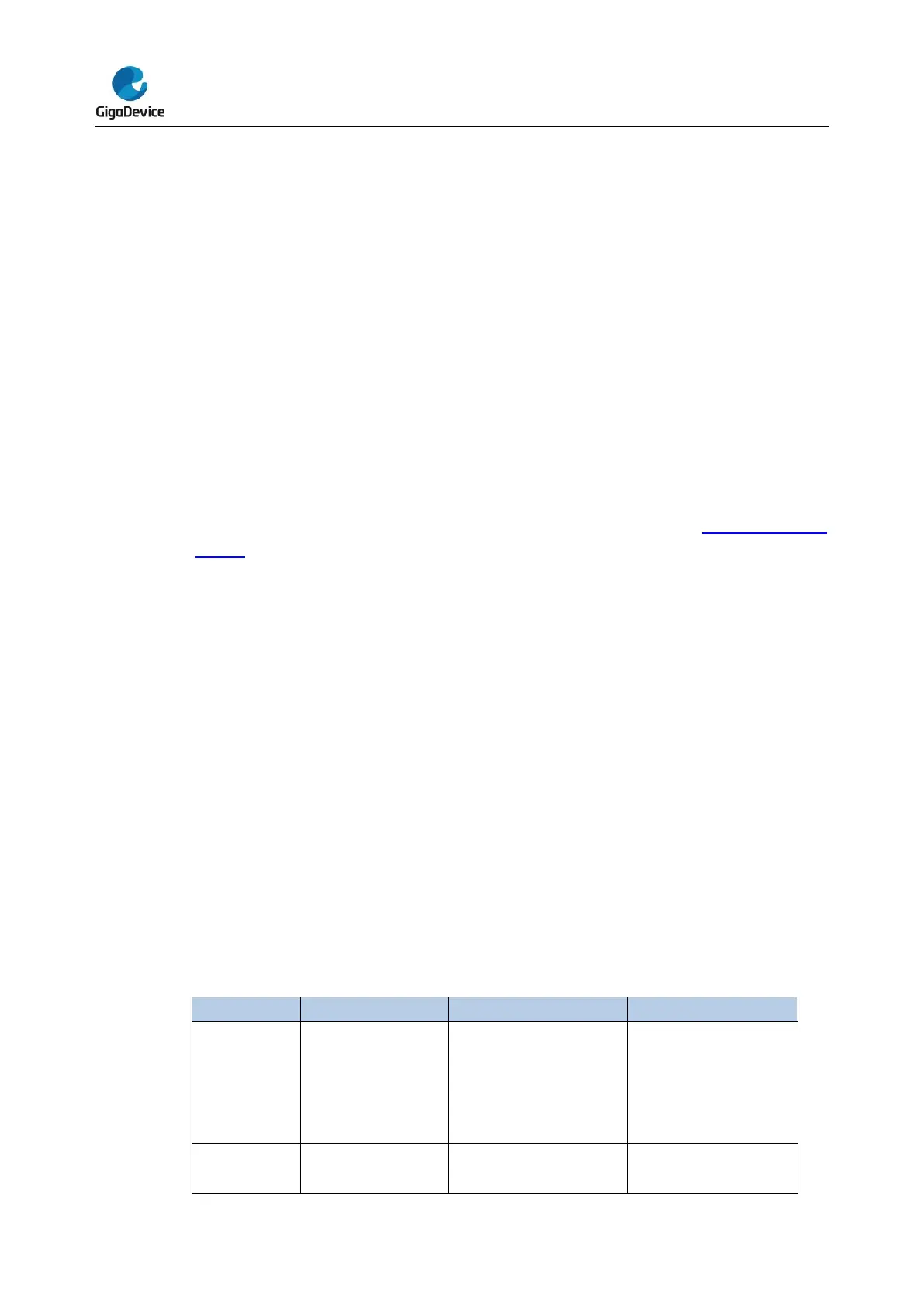

Table 3-1. Power saving mode summary

Loading...

Loading...