Backup domain reset

A backup domain reset is generated by setting the BKPRST bit in the Backup domain control

register or Backup domain power on reset (V

DD

or V

BAT

power on, if both supplies have

previously been powered off).

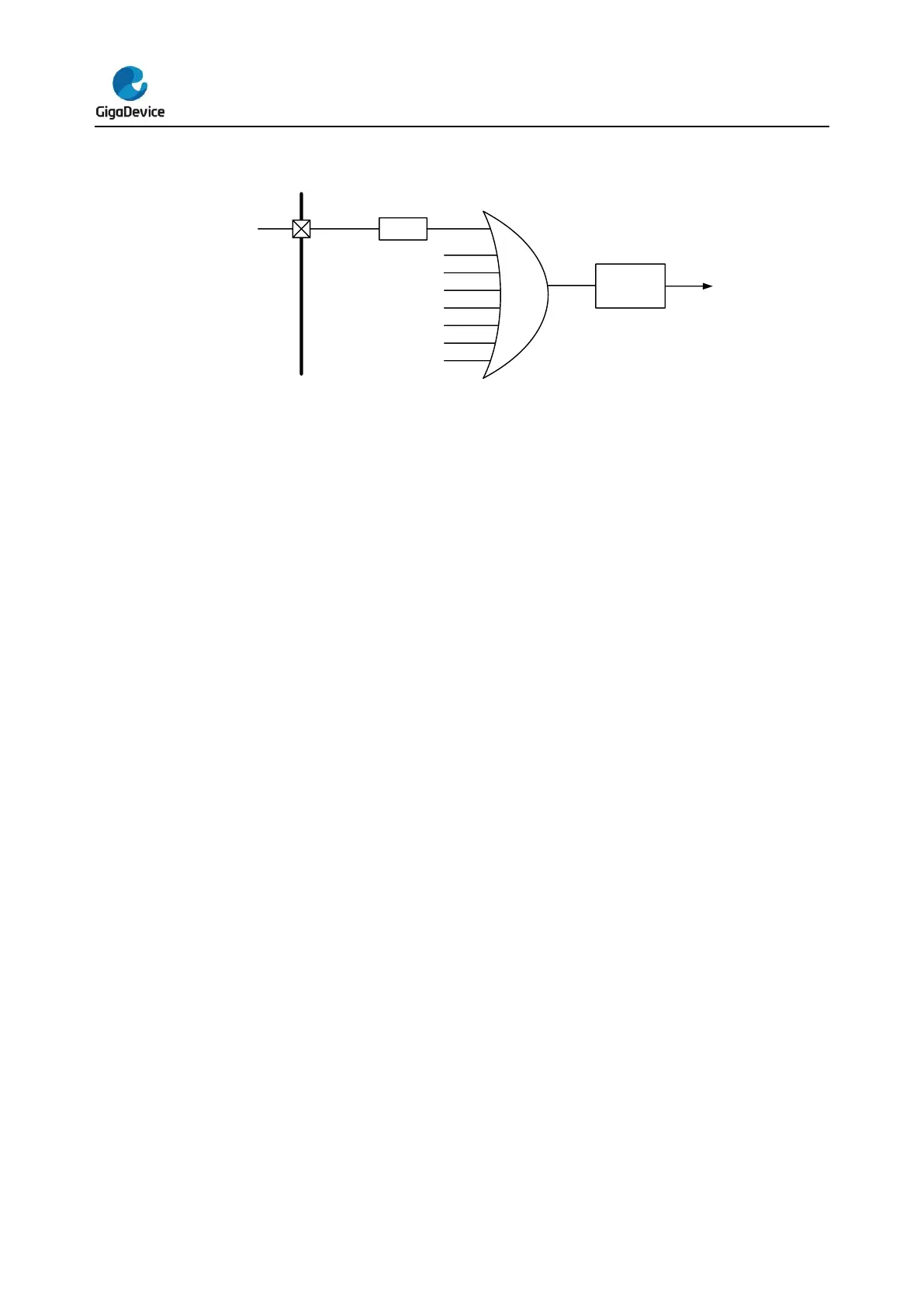

4.2. Clock control unit (CCTL)

4.2.1. Overview

The clock control unit provides a range of frequencies and clock functions. These include an

Internal 8 MHz RC oscillator (IRC8M), an Internal 48M RC oscillator (IRC48M), an Internal

28 MHz RC oscillator (IRC28M), a High speed crystal oscillator (HXTAL), internal 40KHz RC

oscillator (IRC40K), a Low speed crystal oscillator (LXTAL), a Phase Lock Loop (PLL), a

HXTAL clock monitor, clock prescalers, clock multiplexers and clock gating circuitry.

The clocks of the AHB, APB and Cortex

®

-M4 are derived from the system clock (CK_SYS)

which can source from the IRC8M, HXTAL or PLL. The maximum operating frequency of the

system clock (CK_SYS) can be up to 108 MHz. The Free Watchdog Timer has independent

clock source (IRC40K), and Real Time Clock (RTC) use the IRC40K, LXTALor HXTAL/32 as

its clock source.

Loading...

Loading...