sent but not received the ACK from slave.

1: In slave mode, address is received and matches witih its own address. In master

mode, address has been sent and receives the ACK from slave.

START signal is sent out in master mode

This bit is set by hardware and cleared by reading I2C_STAT0 and writing

I2C_DATA.

0: No START signal sent

1: START signal sent

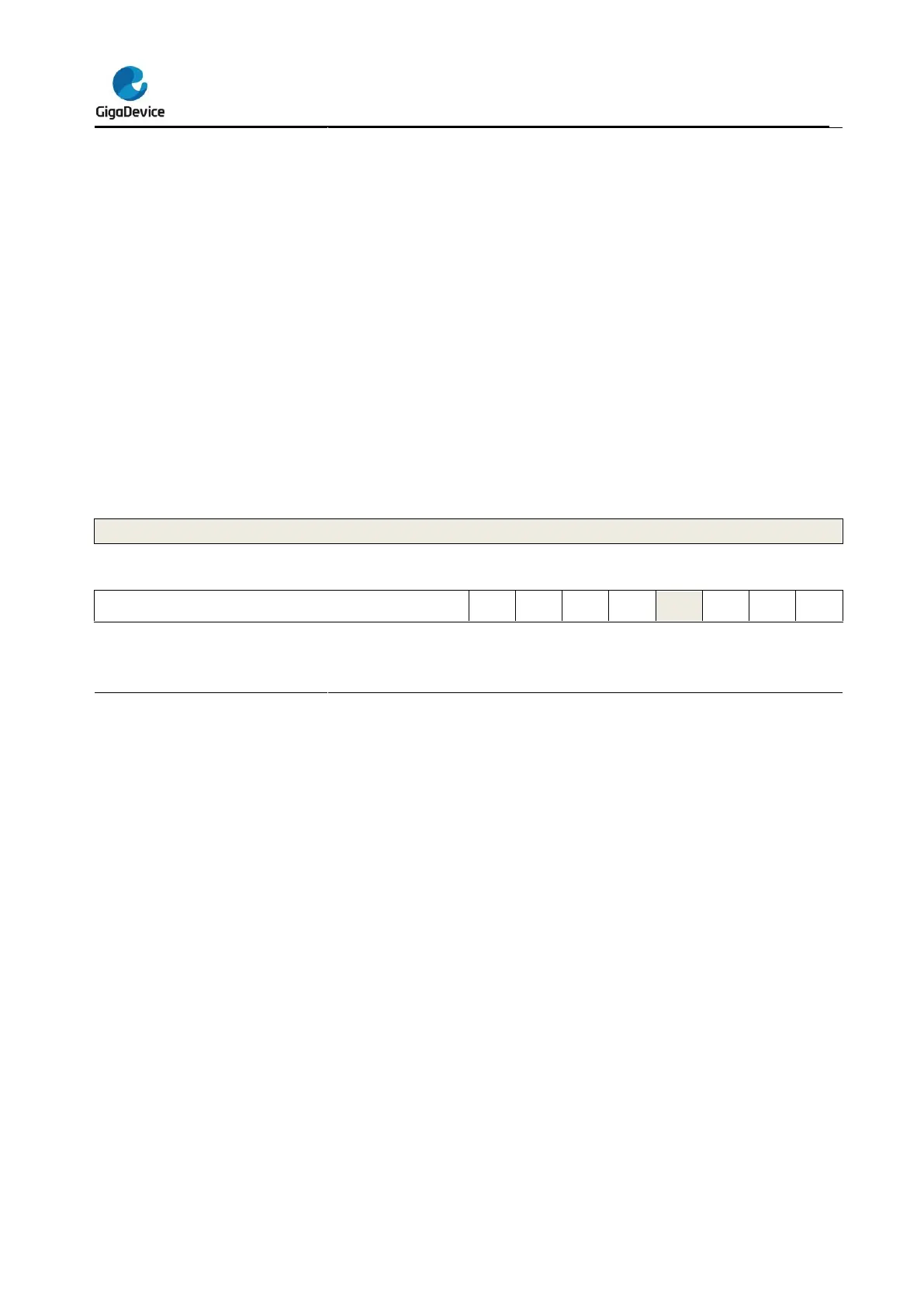

19.4.7. Transfer status register 1 (I2C_STAT1)

Address offset: 0x18

Reset value: 0x0000 0000

This register can be accessed by half-word (16-bit) or word (32-bit).

Must be kept at reset value.

Packet Error Checking value that calculated by hardware when PEC is enabled.

Dual flag in slave mode indicates which address matches with the address in

Dual-Address mode

This bit is cleared by hardware after a STOP or a START signal or I2CEN=0

0: The address matches with SADDR0 address

1: The address matches with SADDR1 address

SMBus host header detected in slave mode

This bit is cleared by hardware after a STOP or a START signal or I2CEN=0

0: No SMBus host header is detected

1: SMBus host header is detected

Default address of SMBus device

This bit is cleared by hardware after a STOP or a START signal or I2CEN=0.

0: The default address has not been received for SMBus device

1: The default address has been received for SMBus device

General call address (0x00) received.

This bit is cleared by hardware after a STOP or a START signal or I2CEN=0.

0: No general call address (0x00) received

Loading...

Loading...