GD32F3x0 User Manual

356

16.3.5. Register definition

TIMER13 base address: 0x4000 2000

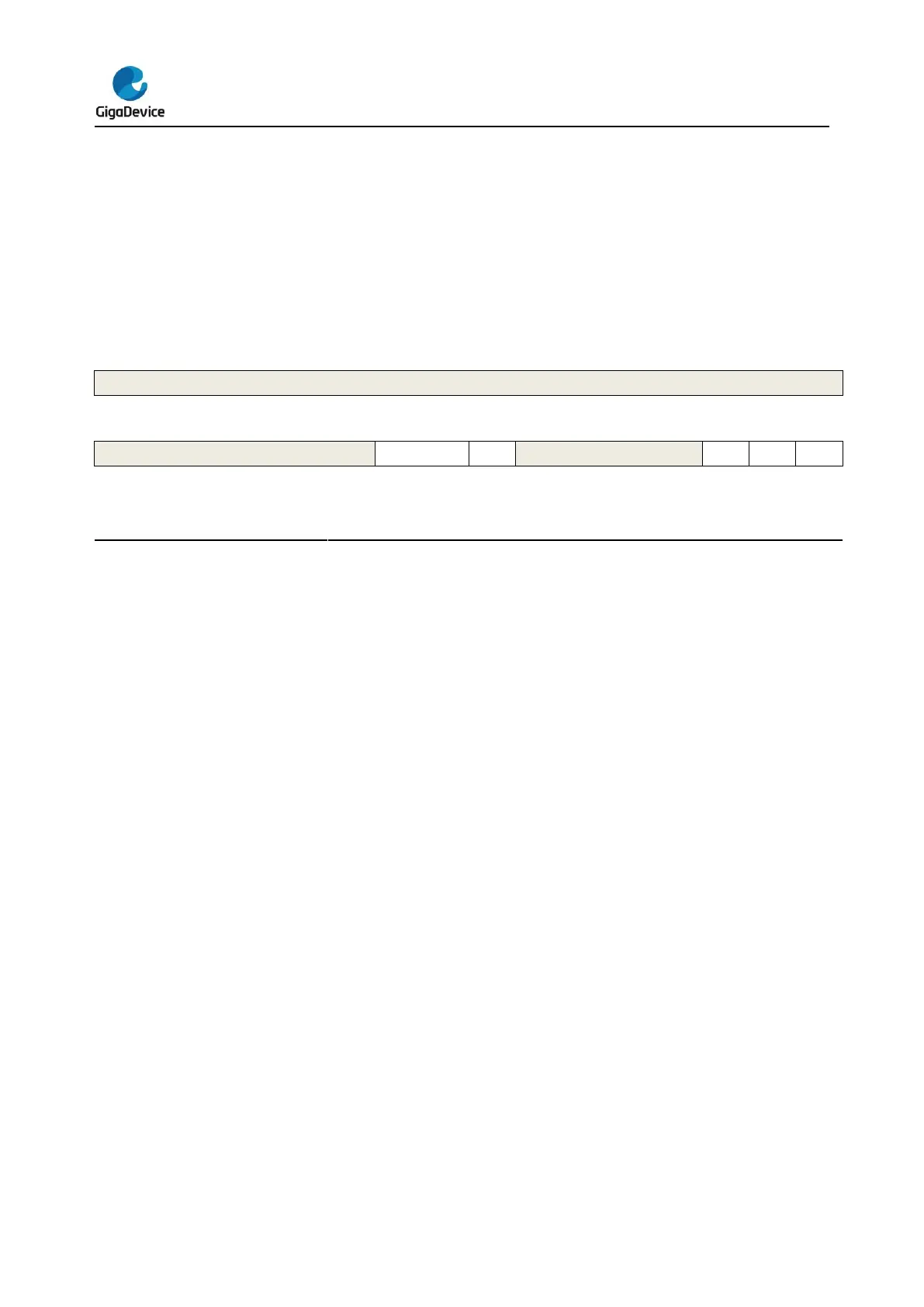

Control register 0 (TIMERx_CTL0)

Address offset: 0x00

Reset value: 0x0000 0000

This register has to be accessed by word (32-bit).

Must be kept at reset value.

Clock division

The CKDIV bits can be configured by software to specify division factor between

the CK_TIMER and the dead-time and digital filter sample clock (DTS).

00: f

DTS

=f

CK_TIMER

01: f

DTS

= f

CK_TIMER

/2

10: f

DTS

= f

CK_TIMER

/4

11: Reserved

Auto-reload shadow enable

0: The shadow register for TIMERx_CAR register is disabled

1: The shadow register for TIMERx_CAR register is enabled

Must be kept at reset value.

Update source

This bit is used to select the update event sources by software.

0: These events generate update interrupts or DMA requests:

The UPG bit is set

The counter generates an overflow or underflow event

The restart mode generates an update event.

1: This event generates update interrupts or DMA requests:

The counter generates an overflow or underflow event

Update disable.

This bit is used to enable or disable the update event generation.

0: Update event enable. When an update event occurs, the corresponding shadow

registers are loaded with their preloaded values. These events generate update

Loading...

Loading...