0: I2C is disabled

1: I2C is enabled

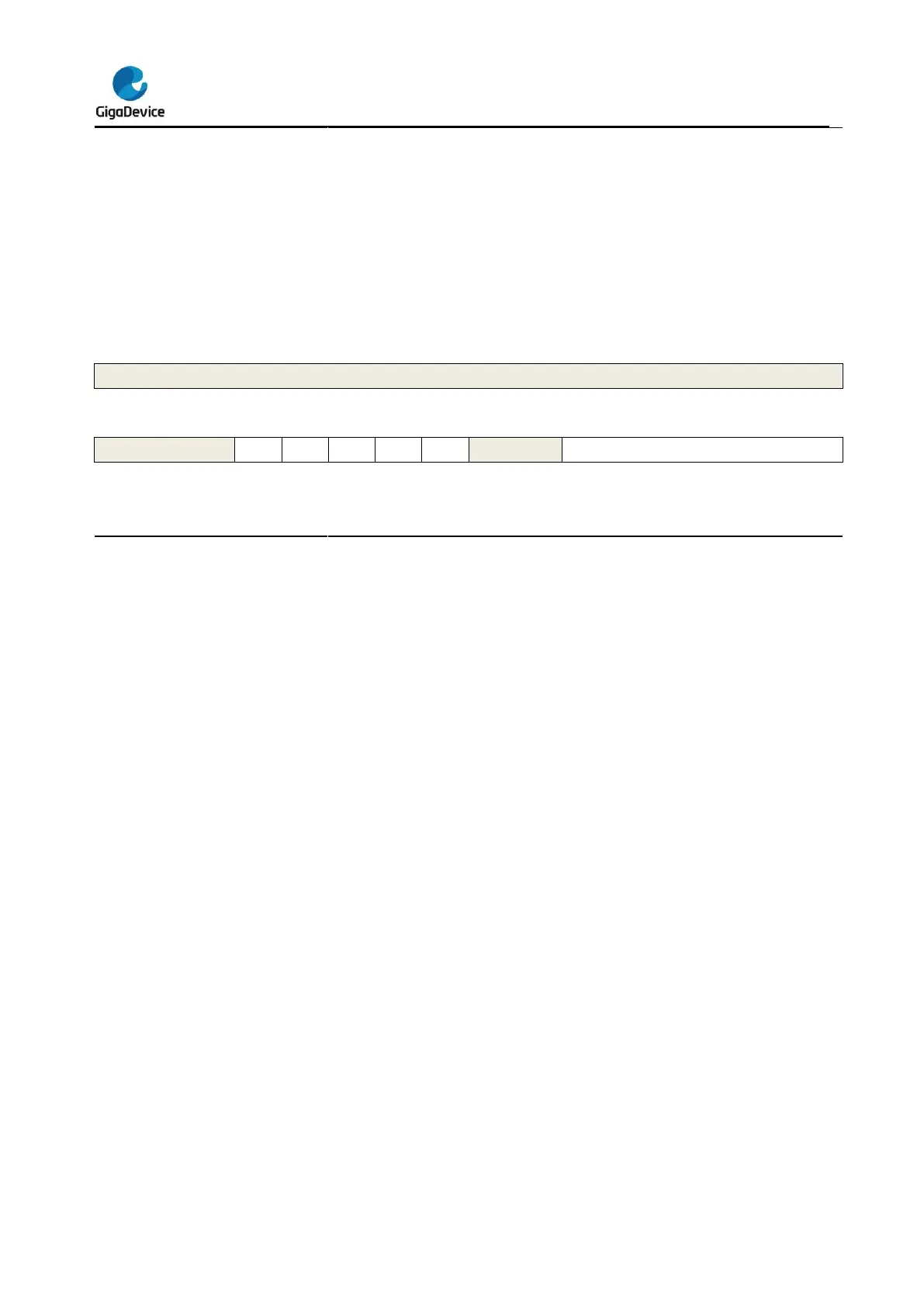

19.4.2. Control register 1 (I2C_CTL1)

Address offset: 0x04

Reset value: 0x0000 0000

This register can be accessed by half-word(16-bit) or word (32-bit).

Must be kept at reset value.

DMA last transfer configure

0: Next DMA EOT is not the last transfer

1: Next DMA EOT is the last transfer

DMA mode switch

0: DMA mode switched off

1: DMA mode switched on

Buffer interrupt enable

0: Buffer interrupt is disabled, TBE = 1 or RBNE = 1 when EVIE=1 will not generate

an interrupt.

1: Buffer interrupt is enabled, which means that interrupt will be generated when

TBE = 1 or RBNE = 1 if EVIE=1.

Event interrupt enable

0: Event interrupt is disabled

1: Event interrupt is enabled, which means that interrupt will be generated when

SBSEND, ADDSEND, ADD10SEND, STPDET or BTC flag asserted or TBE=1 or

RBNE=1 if BUFIE=1.

Error interrupt enable

0: Error interrupt is disabled

1: Error interrupt is enabled, which means that interrupt will be generated when

BERR, LOSTARB, AERR, OUERR, PECERR, SMBTO or SMBALT flag is

asserted.

Must be kept at reset value.

Loading...

Loading...