Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 122

System Memory Interface (DIMM)—Intel

®

EP80579 Integrated Processor Product Line

Board Routing Guidelines

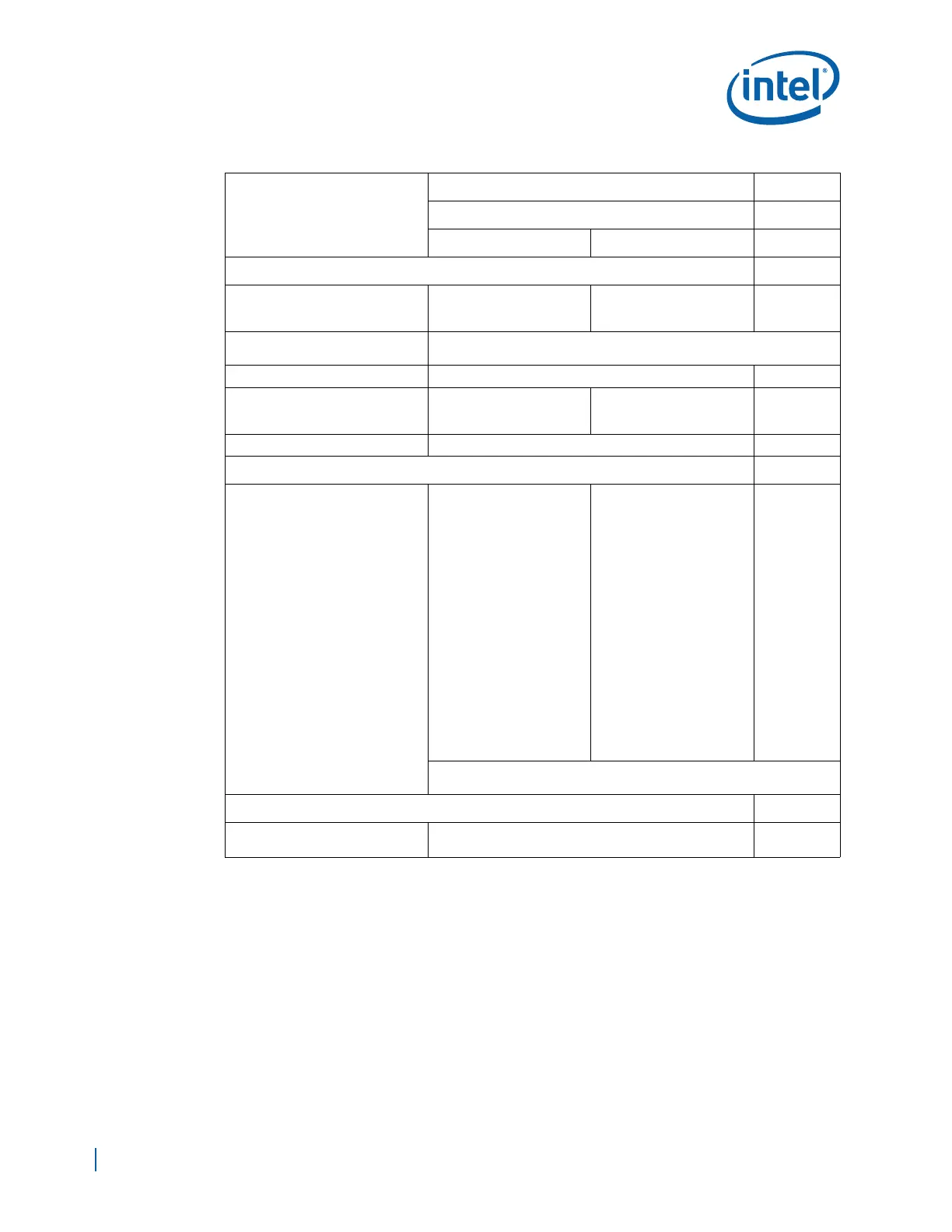

Total Trace Length (TTL) = (L

PKG

+

L

BREAK

+ L

ROUTE

+ L

D2D

)

2.0 in - 6.0 in

Max TTL (DQS/DQS#) =

Min TTL (DQ/DM) +

400 mils

Figure 77

L

PKG

See the Intel

®

EP80579 Integrated Processor Product Line Datasheet for

package length information.

L

BREAK

B = 0.8 in (max)

L

ROUTE

C = 2.0 in - 4.0 in

Calculate while taking into

account Strobe Max Trace

Length (Max TTL)

L

D2D

D = 0.8 in (max) (including both DIMMs’ break-in fields)

Length/Skew Matching Rules

Length Tuning Requirements

• Only length matching

is required within each

Byte lane. No signal

length matching is

required outside the

Byte lane. For

example, any signal

within Data Byte Lane

0 (DQ [0...7]) need not

be length matched to

DQS1

•DQ/DM should match

each other to 20 mils

or less within the same

byte lane. (See

Figure 78)

• The trace length

difference between

DQS and DQS# should

not be more than 10

mils. - that is,

DQS[x] =

DQS[x]#±10 mils, x = 0..

8

• Length match the data

strobes (DQS/DQS#)

to the associated data

mask and data (DQ/

DM) signals for each

Data Byte Lane:

Max(DQS/DQS#) =

Min(DQ/DM[x]) +

400 mils, x = 0.. 8

• Length match all DIMM-to-DIMM (D2D) signals (DQ/DM/DQS/DQS#)

to 10 mils or less within the same byte lane

Routing Rules

Layer Routing Requirements

Signals within a data byte lane must be routed on the

same layer.

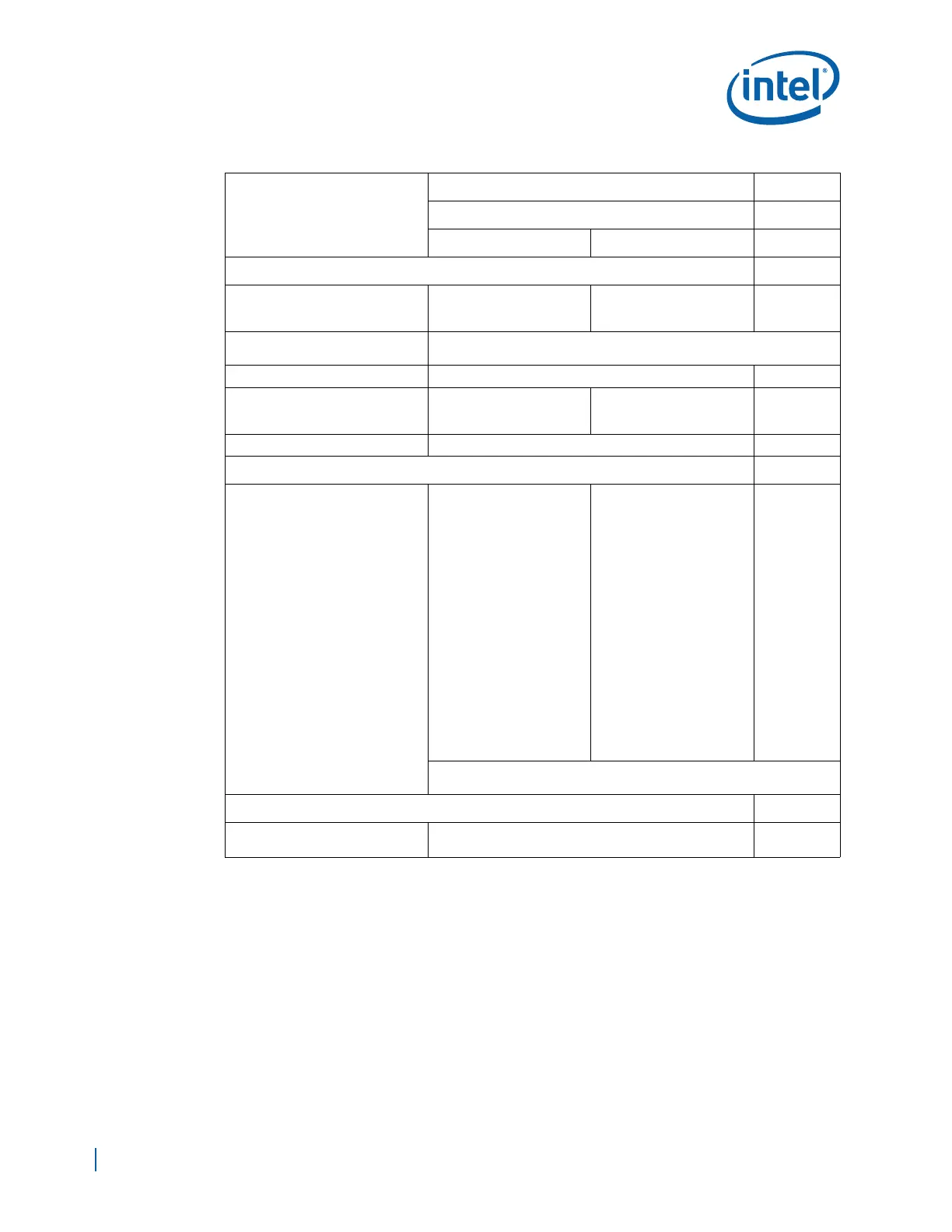

Table 39. Data and Strobe Signal Group Routing Guidelines (Sheet 2 of 2)

Parameter

Routing Guidelines Figure

Data Byte Lane

Data & Data Mask Strobe

Loading...

Loading...