Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 224

Gigabit Ethernet (GbE) Interface—Intel

®

EP80579 Integrated Processor Product Line

19.6.2.2 GbE Receive Data\Control Topology

The receive signals included in the GbE receive Data and Control topology (Figure 141)

are:

—GBEn_RXCTL

— GBEn_RXDATA[3:0]

All the receive path Data and Control signals in a channel (see Figure 141) should be

length matched, routed on the same layer, and referenced to the Receive Clock in

section Section 19.6.2.1. The signals do not need to be length matched between

channels, only within a channel. Table 86 provides routing guidelines for the Receive

Interface signals.

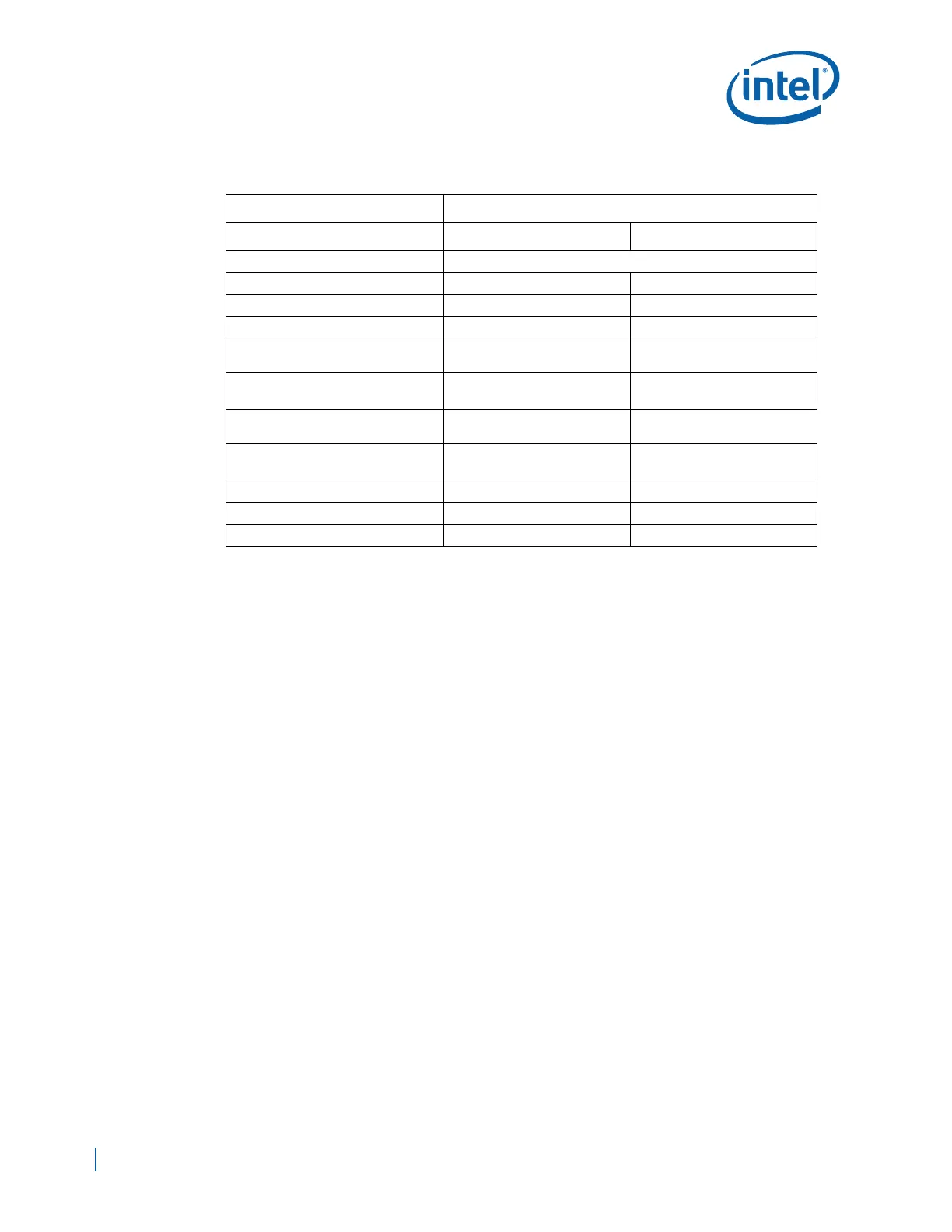

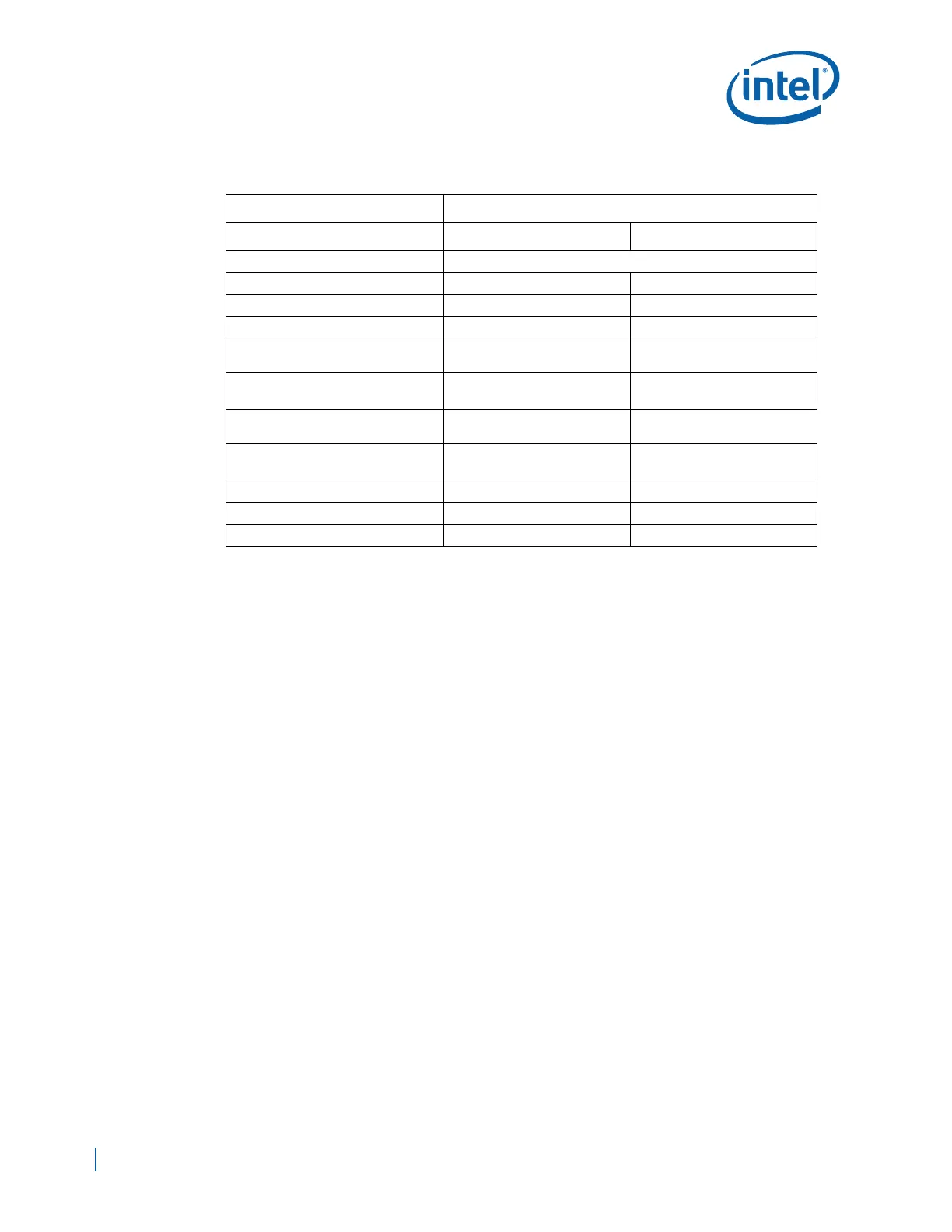

Table 85. GbE RGMII Receive Path Clock Routing Guidelines

Parameter Routing Constraints

Routing Layer Stripline Microstrip

Reference Plane Ground Reference

Board Trace Impedance 50 Ω 50 Ω

Trace Width 4.5mils (L3/L8) 5.5mils (L1/L10)

Clock Spacing (e2e) 20 mils (min) 25 mils (min)

PHY Clock Rx Breakout Length

(LClk_Brk_out_rx)

0.5 inch (max) 0.5 inch (max)

Clock Rx Board Length

(LClk_Brd_route_rx)

min =1.0 inch

max = 7.0 inch

min =1.0 inch

max = 7.0 inch

EP80579 Clock Tx Breakin Length

(LClk_Brk_in_rx)

0.3 inch (max) 0.3 inch (max)

Total Tx Clock Routing (LClk_total_rx)

min =1.0 inch

max = 7.8 inch

min =1.0 inch

max = 7.8 inch

Pull Up Resistor T-Line (Lpull_up) 0.625 inch (max) 0.625 inch (max)

Pull Up Resistor (Rpull_up) 1.2 KΩ (5%) 1.2 KΩ (5%)

Breakout\Breakin Spacing (e2e) 4 mils (min) 4 mils (min)

Loading...

Loading...