Intel

®

EP80579 Integrated Processor Product Line—Gigabit Ethernet (GbE) Interface

Intel

®

EP80579 Integrated Processor Product Line

Platform Design Guide May 2010

225 Order Number: 320068-005US

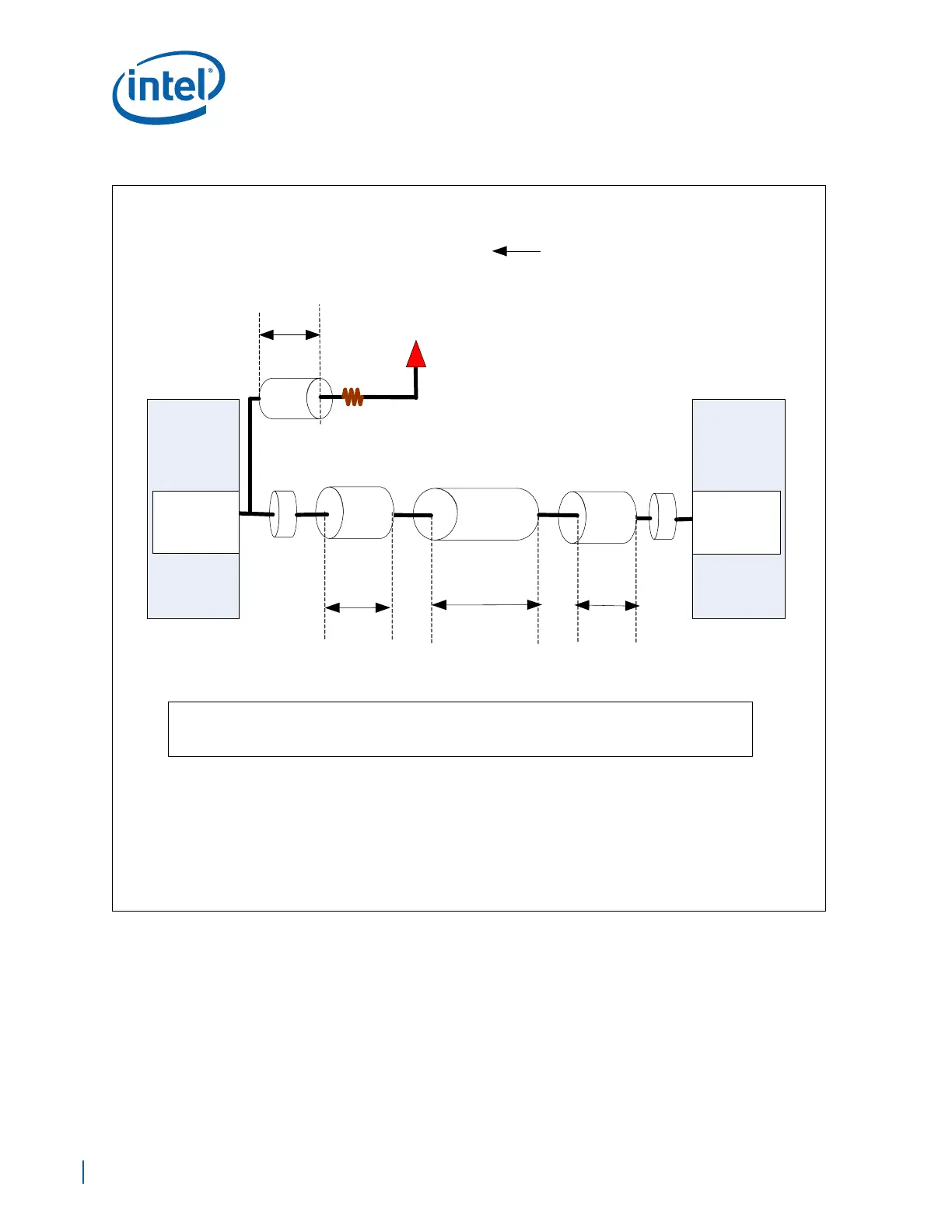

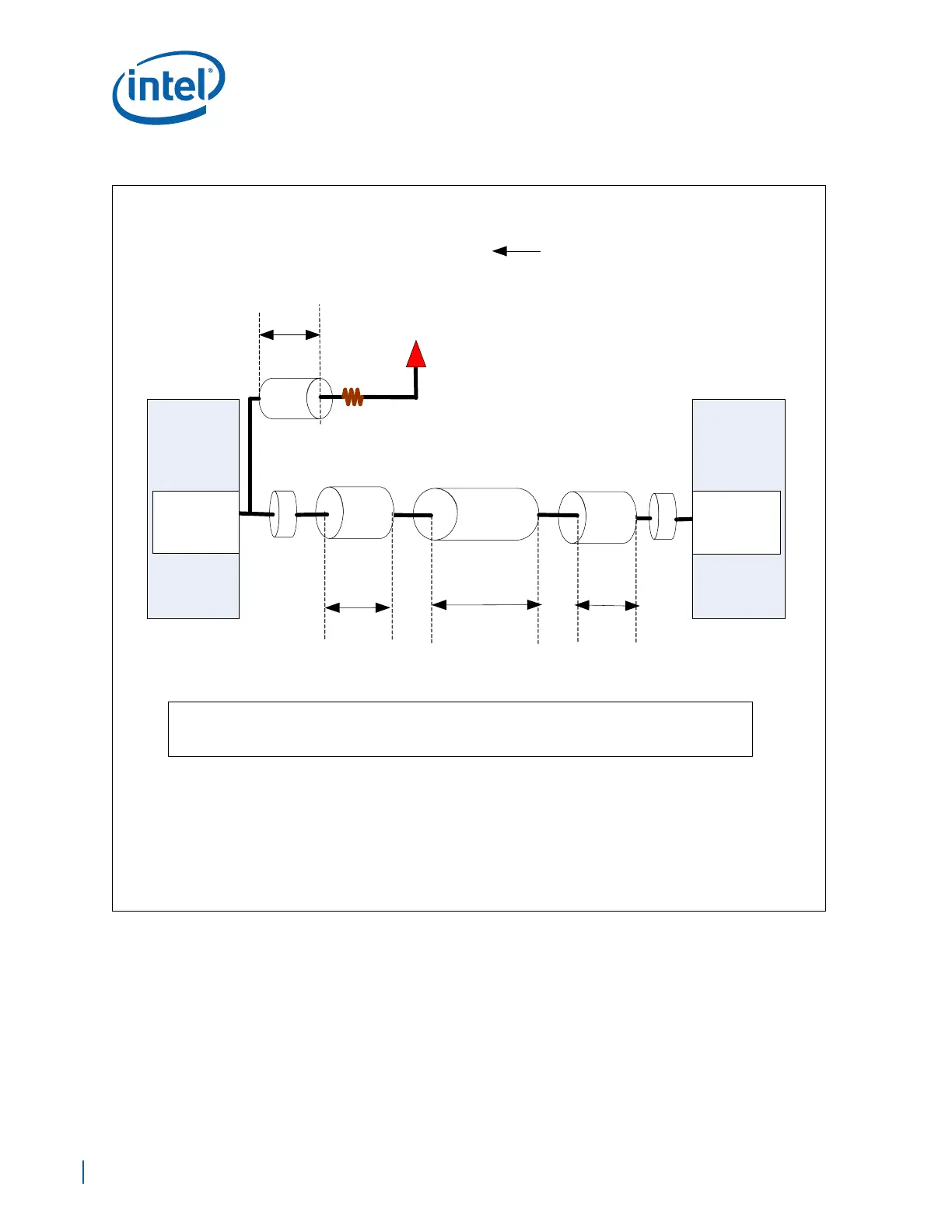

Figure 141. GbE RGMII Receive Path Data/Clock/Control Topology

V2P5

Via

Break in

Break out Board

Receiver

(Data\Ctrl)

PHYEP80579

LD/C_Brk_in_rx LD\C_Brd_route_rx LD\C_Brk_out_rx

L

Pull_up

LD\C_Brk_out_rx + LD\C_Brd_route_rx + LD\C_Brk_in_rxLD\C_Total_rx =

NOTE: Breakout\ Breakin descriptions are as follows:

1. Routing where trace is 3.75 mil wide and 4mil spacing is implemented to escape\ enter BGA

2. The Breakout \ Breakin Length is defined from the pin of the BGA, to where 4 mil spacing

increases to the required spacing per SI recommendations.

Transmitter

(Data\Ctrl)

Via

RGMII Receive Path Data\Control Topology

(EP80579 PHY)

Pull Up

TL (μs)

Rpull up

a). Data\Ctrl = 12 mil edge-to-edge (e2e) for Stripline

b). Data\Ctrl = 18 mil edge-to-edge (e2e) for Microstrip

Loading...

Loading...