Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 85

Power Management and Reset Interface—Intel

®

EP80579 Integrated Processor Product Line

7.1.4 Software Controlled Reset

Software may cause a full system reset through a write to the Reset Control Register

located at I/O port CF9.

7.1.5 CPU (IA-32 core) Only Reset

For power management, error conditions, and other reasons, the EP80579 supports a

targeted CPU only reset semantic. This mechanism eliminates system reset at large

when the CPU function (such as clock gearing selection) must be updated during

initialization. It only affects the CPU. Other blocks such as IICH, IMCH, AIOC complex

are not reset. It is controlled by IMCH.

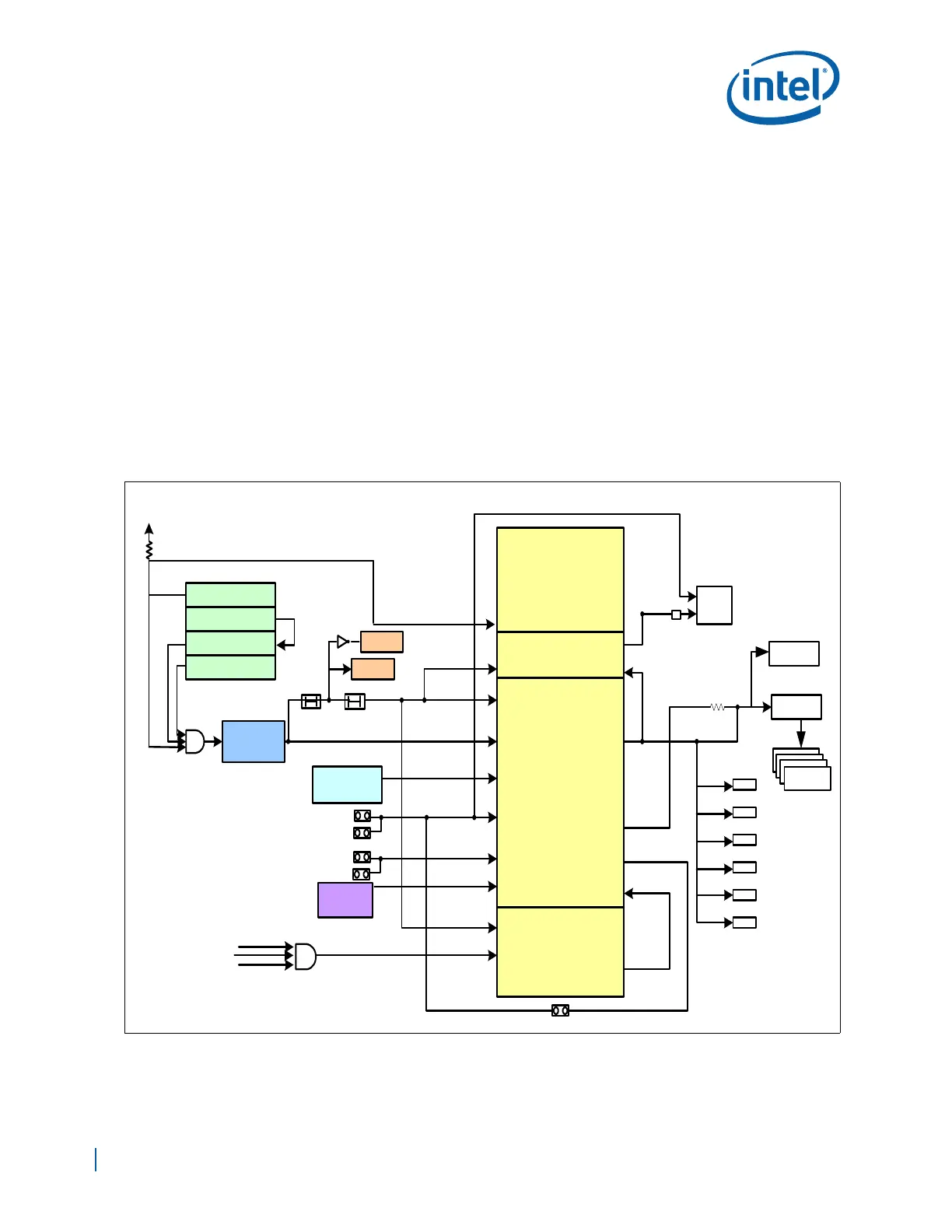

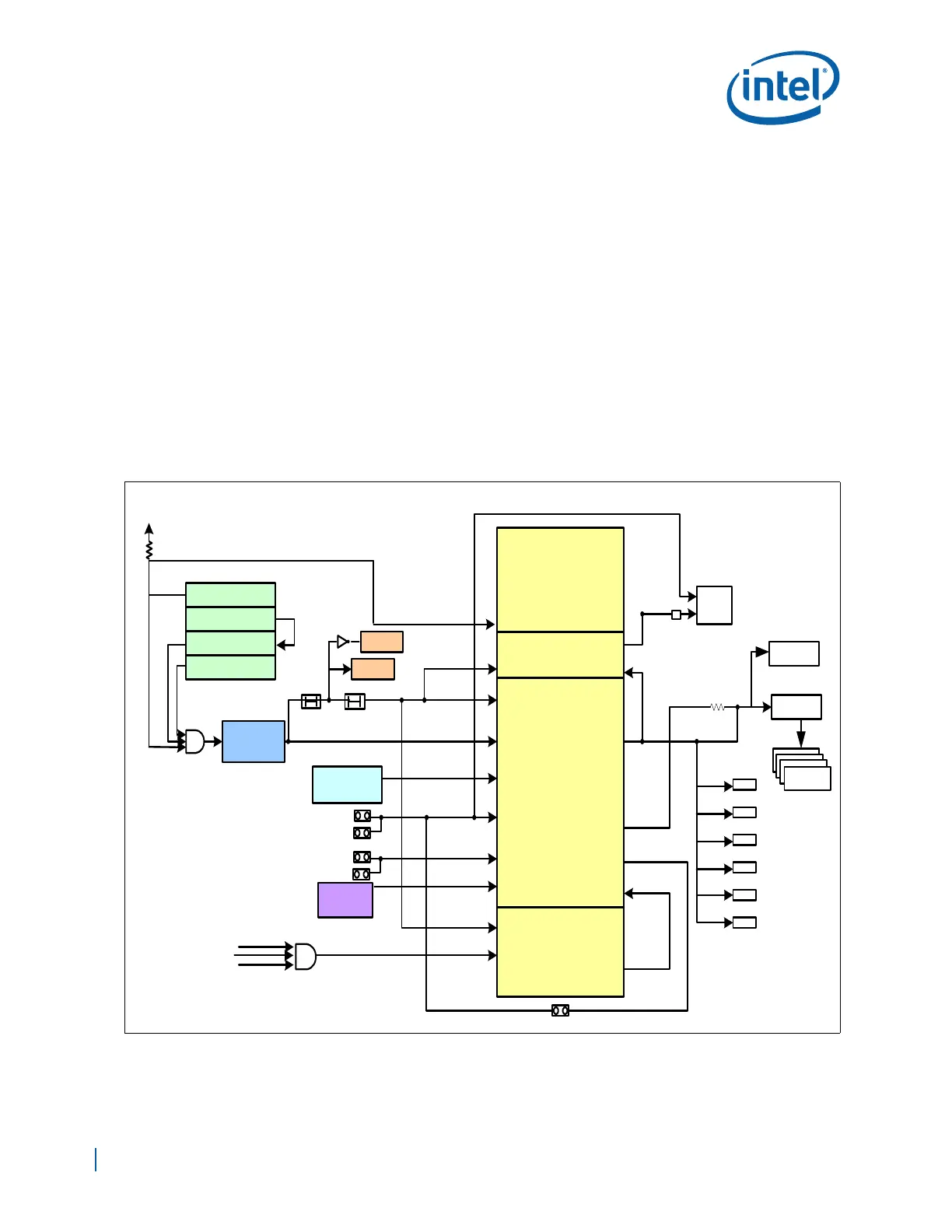

7.2 Reset and Powergood Interface Implementation

This section describes the reset and powergood external interfaces for the EP80579.

Figure 49 provides the block diagram for the reset and powergood interface.

Figure 49. Powergood and Reset Interface

EP80579

WDT _NPWRBTN_N

RSMRST_N

SYS_REST_N

PCIRST_N

PLTRST_N

PWROK

VRMPWRGD

PWRGD RSTI N_N

NC8

RTEST_N

PWRON_BTN

FP_PWRON#

RTCRST#

RTC

RESET_BTN

FP_RESET#

RSMRST#

GLUE 4

CPU_VRD_PWR_GD

SYS_PWR_OK

FWH

LAI

SIO

LPC

P80

PCI-E x4

conn

PCI-E x8 conn

ITP/ XDP

1k

SYS_PWR_OK

GBE _AU X_PWR_ GOOD

GBE_PME_WAKE

GBE_aux_pwr_good

Wake signal

TPM

1.0V/1.3V

IA-32 core

Ready

CK410

2.5V for GbE

1.2V Logic Core

Ready

SILVERBOX_PWROK

GBE Powergood

2ms

Delay

100ms

Del ay

PWRGD

DDR2 1. 8V

PME_N

0 ohm empty

PCI-E switch

D_DRPWROK

Vccsus25 2.5V

Vccpsus 3.3V

Vccsus1 1.2V

EN

EN

DB800

inverter

VSBY3_3

Loading...

Loading...