Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 238

Local Expansion Bus (LEB) Interface—Intel

®

EP80579 Integrated Processor Product Line

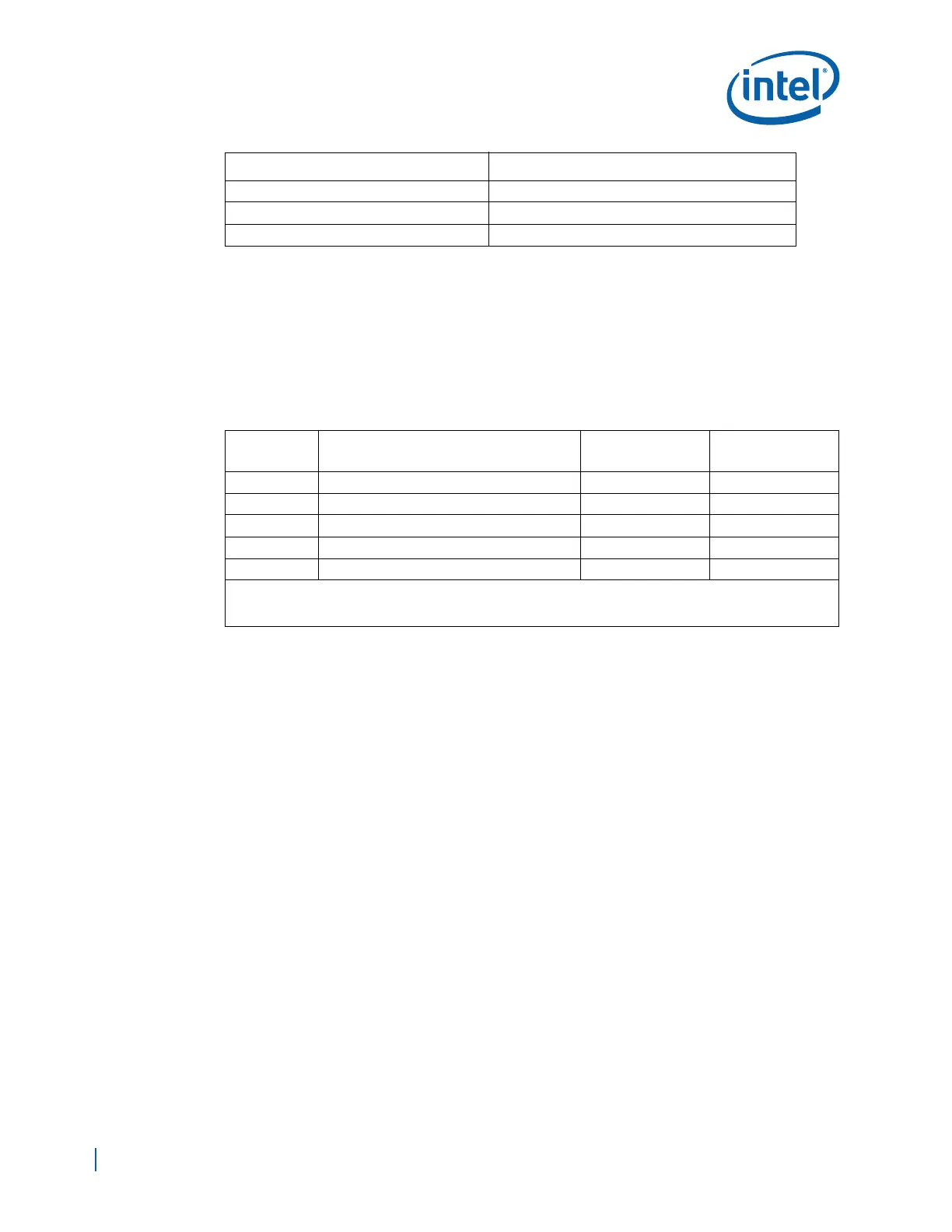

22.2 LEB Memory Size (LEB_SIZE) Strapping

As stated above, the LEB controller allocates up to 256 MB of memory space to support

up to 8 devices on the LEB Bus. At power-up or whenever RESET_IN# is asserted,

EX_ADDR[23:21] bits are captured and stored by the LEB controller to detemine the

LEB memory size (LEB_SIZE) and the number of devices supported on the bus. The

EX_ADDR[23:21] should be externally strapped with 1K ohm pull-ups and pull-downs

to determine the LEB_SIZE as shown in Table 87.

22.3 LEB Interface Topologies

There are three groups of signals that require careful routing when designing with the

LEB interface. These groups are split into Chip Select, Address, and Data/Control

signals. The following sections recommend guidelines to help design a working system

that will minimize signal integrity issues. The recommendations are based on the

Development Board routing with the LEB clock rate at 33 MHz.

22.3.1 LEB Interface Topology at 33 MHz

The Development Board has been designed to interface with up to 7 devices, which are

split in two bridges. The primary bridge interconnects with the first four peripherals and

a buffer, while the secondary bridge interconnects with three mezzanine connectors.

The connectors are to be used to interface with existing line cards and future develop

cards. With careful routing and following the guidelines in this chapter, this topology

can run at a maximum speed of 33 MHz.

EX_CS4# Mezzanine Connector 1

EX_CS5# Mezzanine Connector 2

EX_CS6# Mezzanine Connector 3

Chip Select Signal Peripheral

Table 87. LEB Memory Size (LEB_SIZE) Strapping

LEB_SIZE

[23 : 21]

MMBAR

Size

# of CS

“+ 16 MB” mode

# of CS

“+ 32 MB” mode

000 0 MB None None

001 32 MB 2 1

010 64 MB 4 2

011 128 MB 8 4

1xx 256 MB 16 (See Note) 8

Note: Only 8 chip selects are supported; the other 8 are alias of the first 8 chip selects. Refer to the Utilizing

the Local Expansion Bus on the Intel® EP80579 Integrated Processor Product Line Application Note,

Document Number 321096 for details.

Loading...

Loading...