Intel

®

EP80579 Integrated Processor Product Line—Gigabit Ethernet (GbE) Interface

Intel

®

EP80579 Integrated Processor Product Line

Platform Design Guide May 2010

215 Order Number: 320068-005US

19.5 GbE Interface - LAN Connect Interface Guidelines

The following sections contain guidelines on implementing a platform LAN connect

device on a system motherboard. These sections should treated as a guideline and not

as a specification and the system designer must ensure through simulations or other

techniques that the system meets the specified timings.

19.5.1 GbE Ethernet Interface — RGMII Mode

This section describes the GbE Ethernet reference clock transmit and receive timings

when operating in RGMII mode. RGMII works in source synchronous mode, where

transmit and receive data are synchronized with respect to TxCLK and RxCLK. In RGMII

mode, TxCLK and RxCLK run at 2.5/25/125 MHz. In 2.5/25 MHz mode, both

transmission and receive occurs on rising edges of the clock. At 125 MHz, data transfer

(both Tx and Rx) occurs on both edges of the clock.

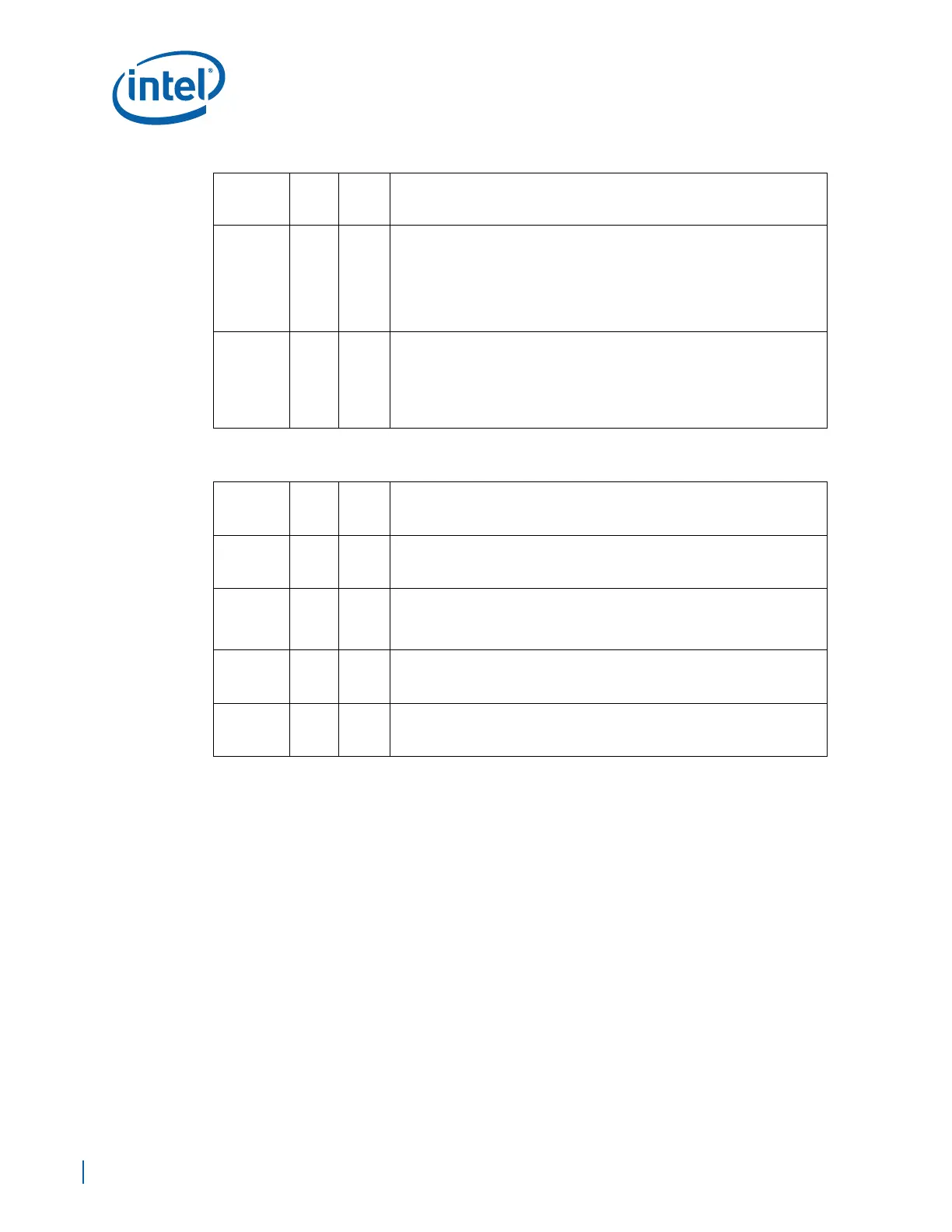

Table 81. GbE MAC Management Data Interface Signals

Name

Input/

Output

Pull

Up/

Down

Recommendations

MDIO IO Yes

• Management Data Input/Output.

• Pull-up signal to EP80579 GbE 2.5V Standby (VCCSUS25) using a 1.5 KΩ

± 5% resistor.

Note:

• Must be pulled high through a 10 KΩ resistor to EP80579 GbE 2.5V

Standby (VCCSUS25) the interface is not used.

MDC O No

• Management Data Clock.

• Provide termination if signal is connected to multiple receivers

• Resides in GbE Standby Power Well

Note:

• Can be left as no connect if the interface is not used.

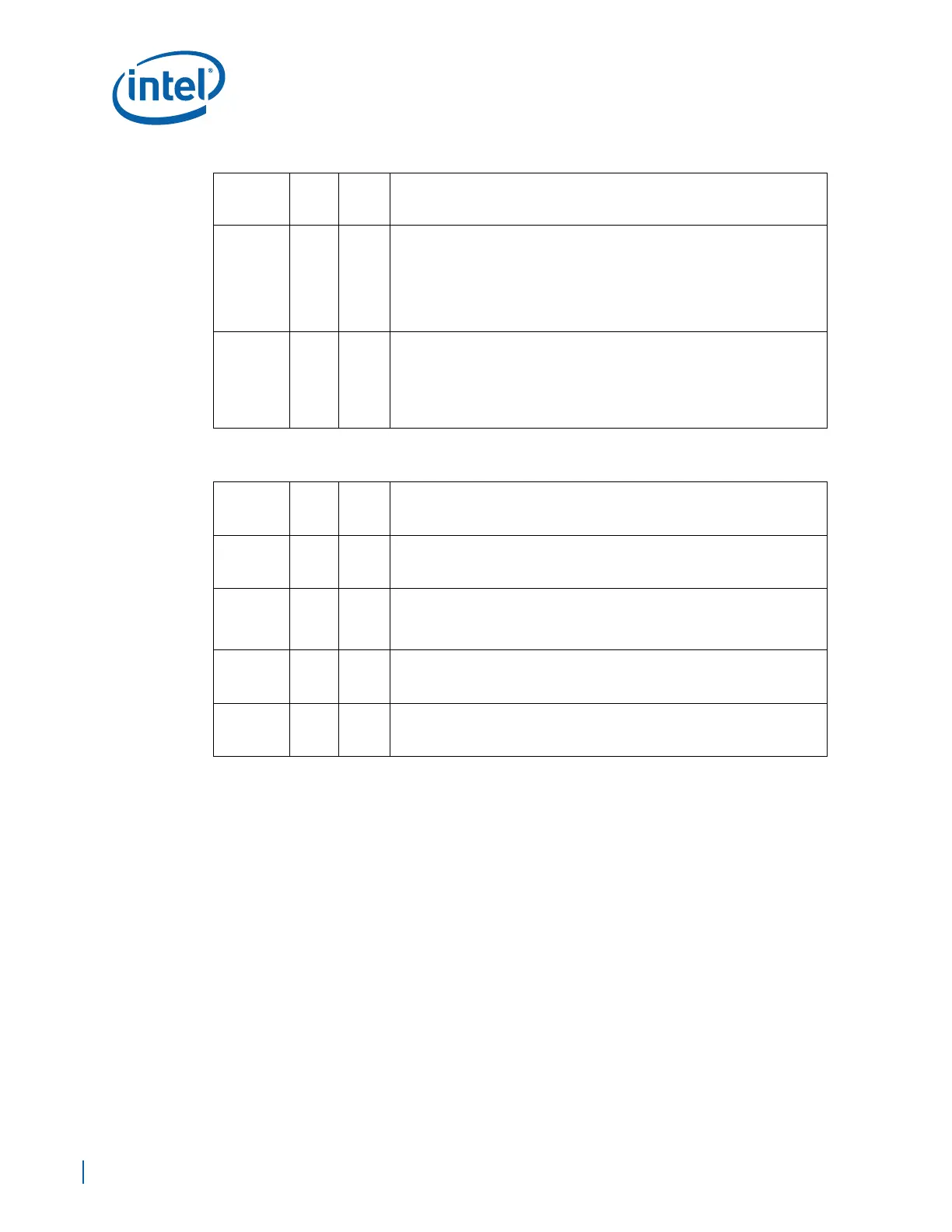

Table 82. GbE MAC Serial EEPROM Interface Signals

Name

Input/

Output

Pull

Up/

Down

Recommendations

EEDO I Yes

• EEPROM Output Data. Data from EEPROM to EP80579

•An external pull-up resistor of 4.7 KΩ is required.

• Resides in GbE Standby Power Well.

EEDI O Yes

• EEPROM Input Data. Data from EP80579 to EEPROM

• Requires a 20KΩ pull-up resistor to GbE Standby Power, if GbE

Standby power is generated on the platform; otherwise pull-down

with 4.7 KΩ

EECS O Yes

• EEPROM Chip Select. Used to enable EEPROM device

•An external pull-down resistor of 4.7 KΩ is required.

• Resides in GbE Standby Power Well.

EESK O Yes

• EEPROM Shift Clock. Clock for the EEPROM Interface (~ 1 MHz)

•An external pull-down resistor of 4.7 KΩ is required.

• Resides in GbE Standby Power Well.

Loading...

Loading...