Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 226

Gigabit Ethernet (GbE) Interface—Intel

®

EP80579 Integrated Processor Product Line

19.7 GbE Serial EEPROM

The GbE MACs use a 4K- bit (256 x 16 bits each) serial EEPROM device for storing

product configuration information. Several EEPROM words are automatically accessed

by the GbE controller after reset to provide pre-boot configuration data before it is

accessed by the host software. The remainder of the stored information is available to

software for storing the MAC addresses and additional configuration information for

three GbE MACs. The EEPROM algorithm programmed into the GbE controllers is

compatible with most commercially available 3.3V Microwire* interfaces, serial EEPROM

devices, with a 256 x 16 organization and a 1 MHz speed rating.

All three controllers share the same EEPROM. A fixed priority arbiter controls access to

the EEPROM where highest priority is given to GbE 0 then GbE 1 and finally GbE 2.

19.8 Wake on LAN

Two types of wake-up mechanisms are supported:

• Advanced Power Management (APM) Wake-up

•ACPI Power Management Wake-up

When so configured, if a wake-up packet is received, the GBE_PME_WAKE signal will be

asserted. The GBE_PME_WAKE signal of all three GbE MACs are wired-or together and

brought to the external pin GBE_PME_WAKE. The user must externally connect this pin

to the PME_N input pin.

19.9 GbE RComp

The GbE RCOMP (Resistive COMPensation) circuitry dynamically compensates the GbE

I/O output drivers for variations in operating conditions due to process, temperature,

voltage and PCB layout. These variations are measured through a resistive mechanism

in two special I/O pads.

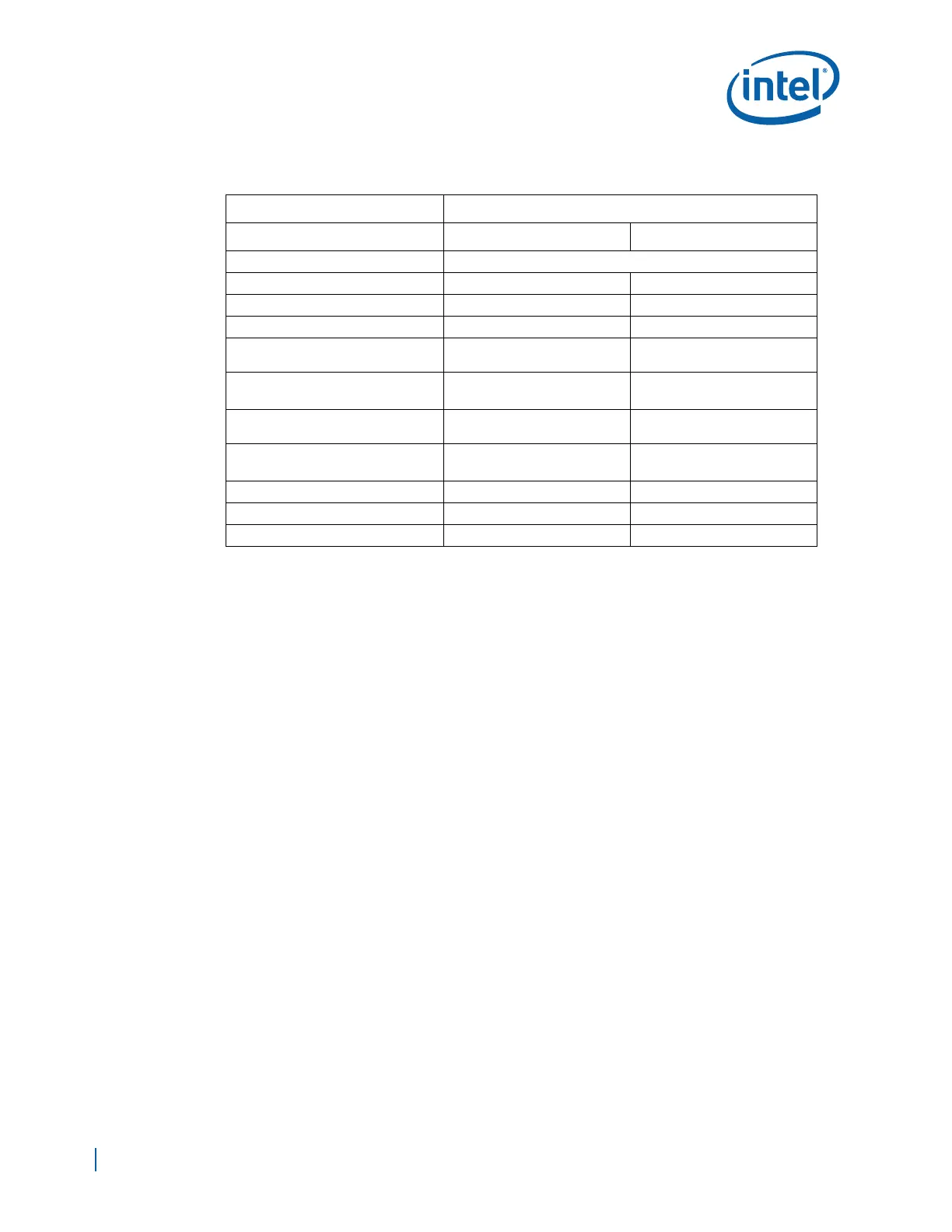

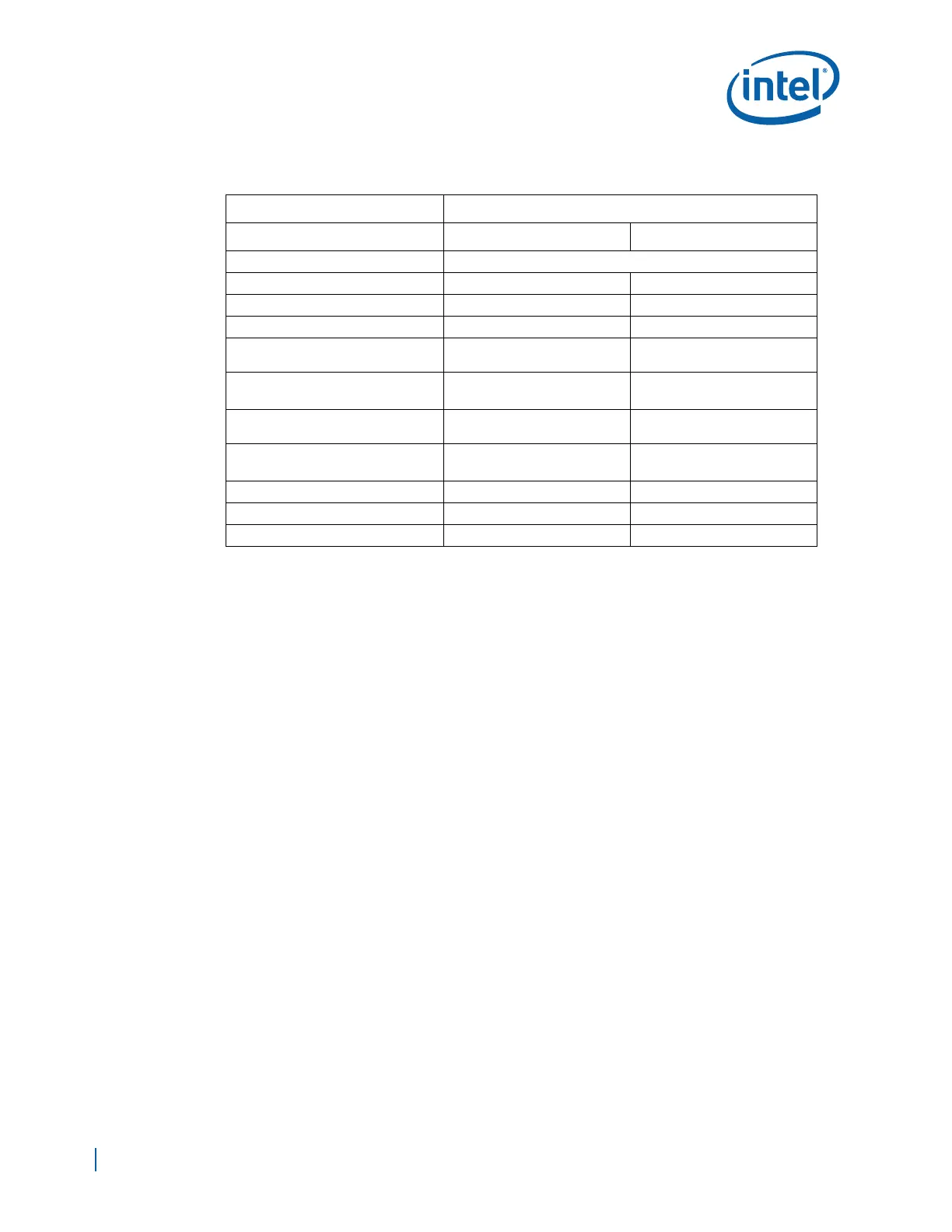

Table 86. GbE RGMII Receive Path Data\Control Routing Guidelines

Parameter Routing Constraints

Routing Layer Stripline Microstrip

Reference Plane Ground Reference

Board Trace Impedance 50 Ω 50 Ω

Trace Width 4.5mils (L3/L8) 5.5mils (L1/L10)

Data\Control Spacing (e2e) 12 mils (min) 18 mils (min)

PHY Data\Control Rx Breakout Length

(LD\C_Brk_out_tx)

0.5 inch (max) 0.5 inch (max)

Data\Control Rx Board Length

(LD\C_Brd_route_rx)

min =1.0 inch

max = 7.0 inch

min =1.0 inch

max = 7.0 inch

EP80579 Data\Control Tx Breakin

Length (LD\C_Brk_in_rx)

0.3 inch (max) 0.3 inch (max)

Total Data\Control Rx Routing

(LD\C_total_rx)

LClk_total_rx ± 50 mils

(See Table 85)

LClk_total_rx ± 50 mils

(See Table 85)

Pull Up Resistor T-Line (Lpull_up) 0.625 inch (max) 0.625 inch (max)

Pull Up Resistor (Rpull_up) 1.2 KΩ (5%)) 1.2 KΩ (5%)

Breakout\Breakin Spacing (e2e) 4 mils (min) 4 mils (min)

Loading...

Loading...