Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 106

Platform System Clock—Intel

®

EP80579 Integrated Processor Product Line

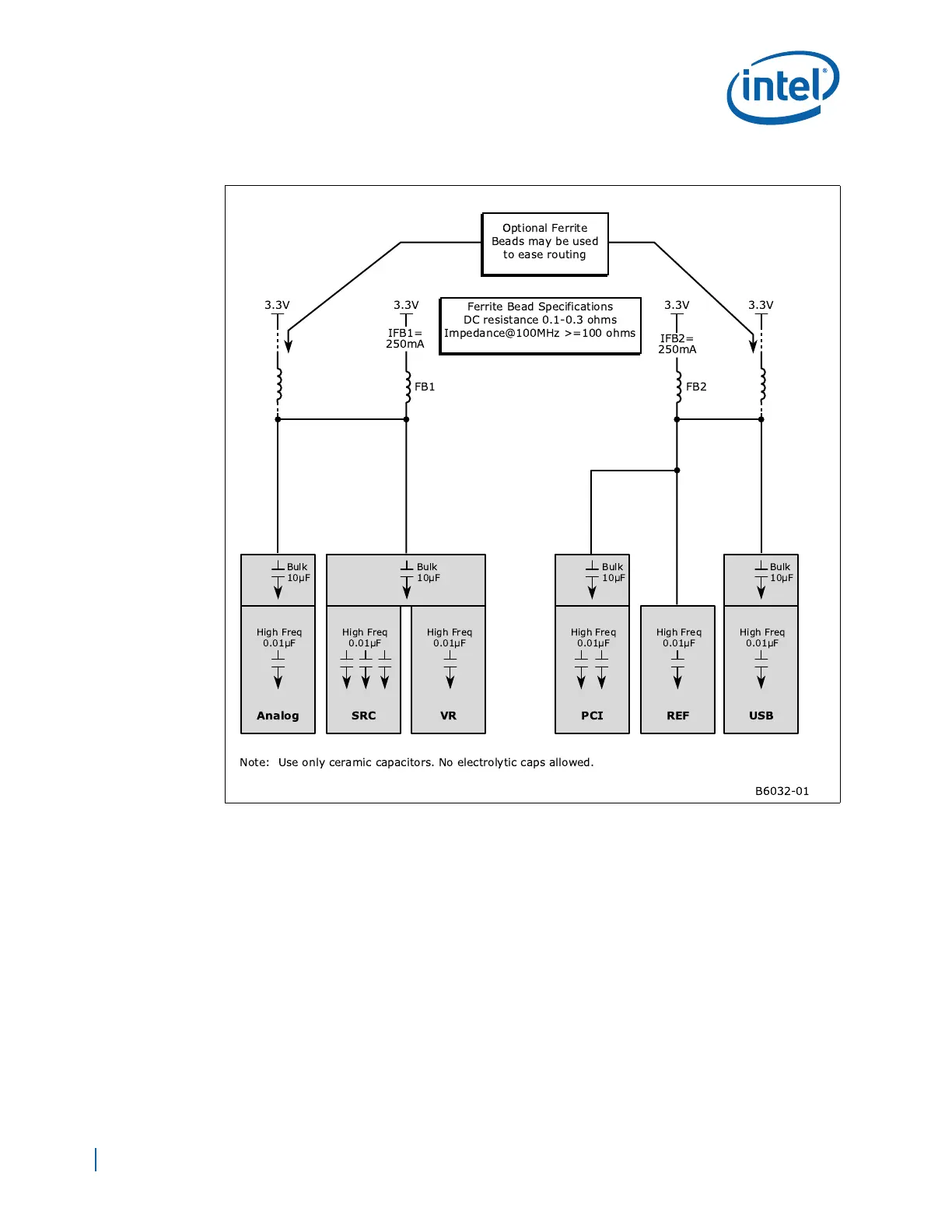

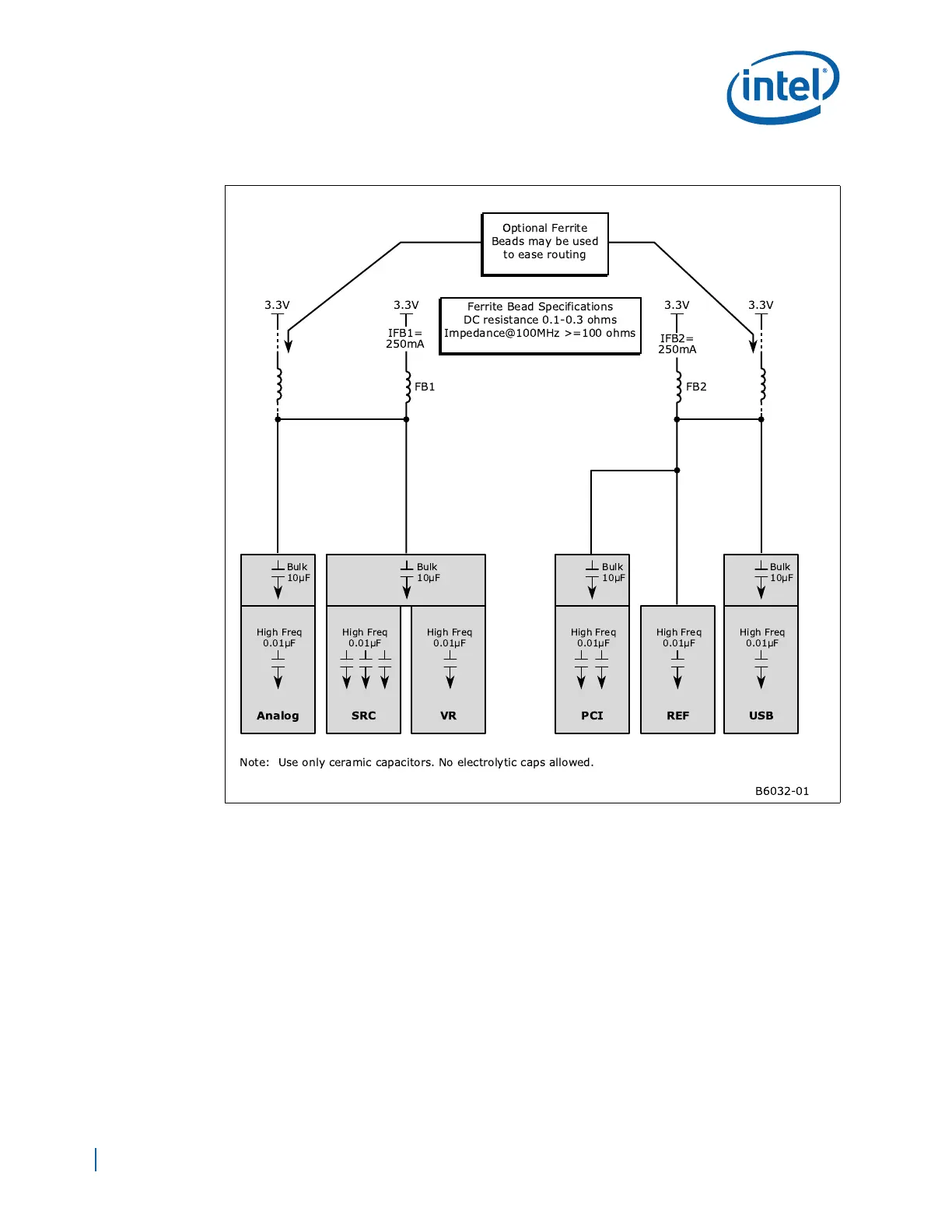

8.3.4 CK410 Power Plane Filtering

8.3.4.1 VDD Plane Filtering

The VDD decoupling requirements for a CK410 compliant clock synthesizer are as

follows:

• One 300 Ω (100 MHz) Ferrite Bead is recommended for the VDD plane.

• 10 µF of bulk decoupling cap in a 1206 package placed close to the VDD generation

circuitry is recommended for the VDD plane. Two 4.7 µF caps can also be used in

place of the 10 µF cap.

• Seven 0.1 µF high-frequency decoupling caps in the 0603 packages should be

placed as close to each VDD pin as possible.

Figure 67. Decoupling and Filtering Per Clock Group

Analog

USB

REF

PCI

SRC

VR

!" # $$ $$ ! $$ $ %

&$'$

() $

*$+,- ./

*/

01

2 2

*/

01

22

Loading...

Loading...