Intel

®

EP80579 Integrated Processor Product Line—General Purpose I/O (GPIO) and Interrupt

Interface

Intel

®

EP80579 Integrated Processor Product Line

Platform Design Guide May 2010

204 Order Number: 320068-005US

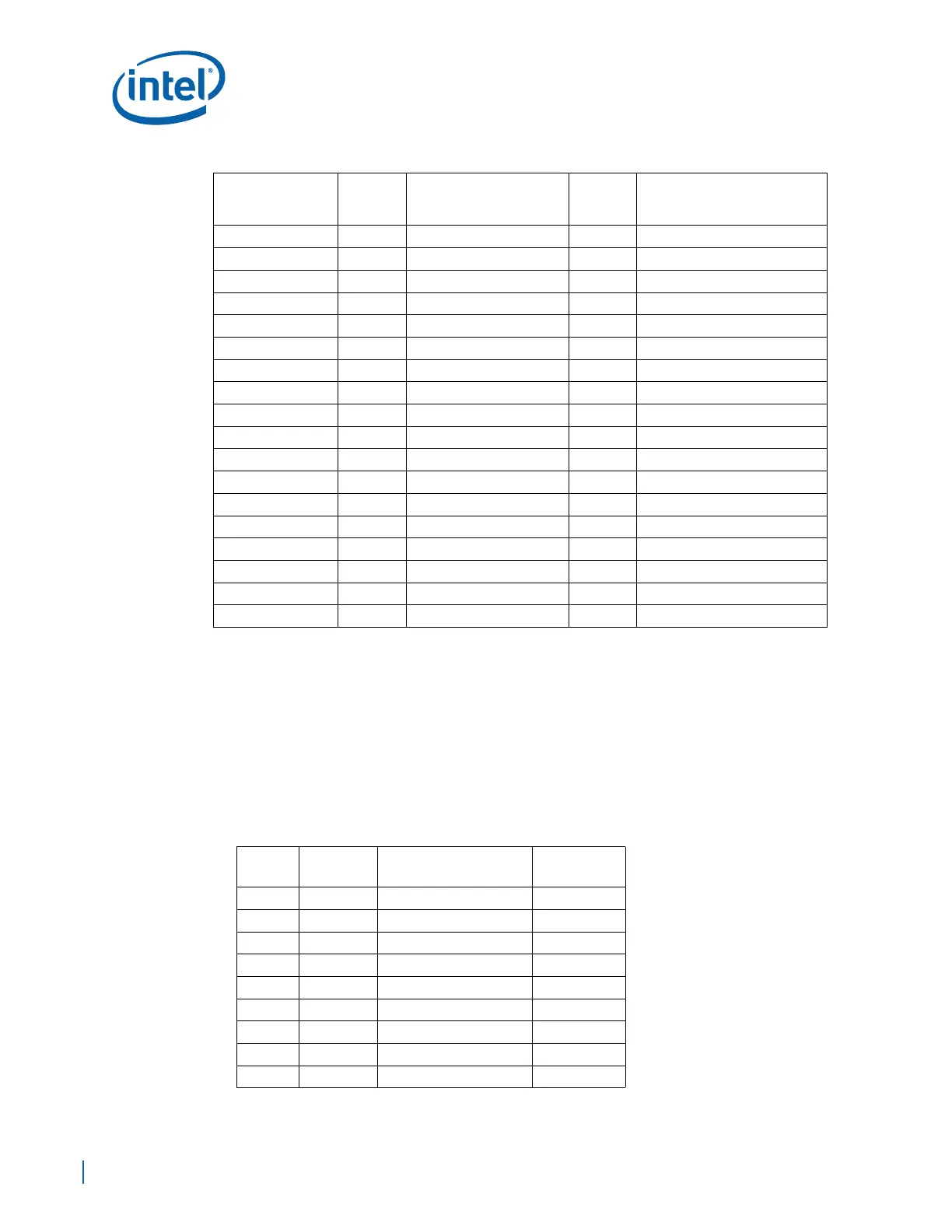

17.2 Interrupts

EP80579 provides support for up to four PCI interrupt pins (PIRQ[E:H]) and PCI 2.3

message-based interrupts. EP80579 also maintains support for ISA (legacy)-style

interrupts via the serial interrupt protocol (SERIRQ). PCI Interrupts (PIRQ[A:D]) are

not pinned out on EP80579, but supported via SERIRQ. When IOAPIC is active,

IRQ[39:24] are externally driven interrupts through GPIO pins, enabled if SIU_TXD2 is

pulled low on power-up.

Table 77 shows the mapping of the various interrupts when the IOAPIC is active.

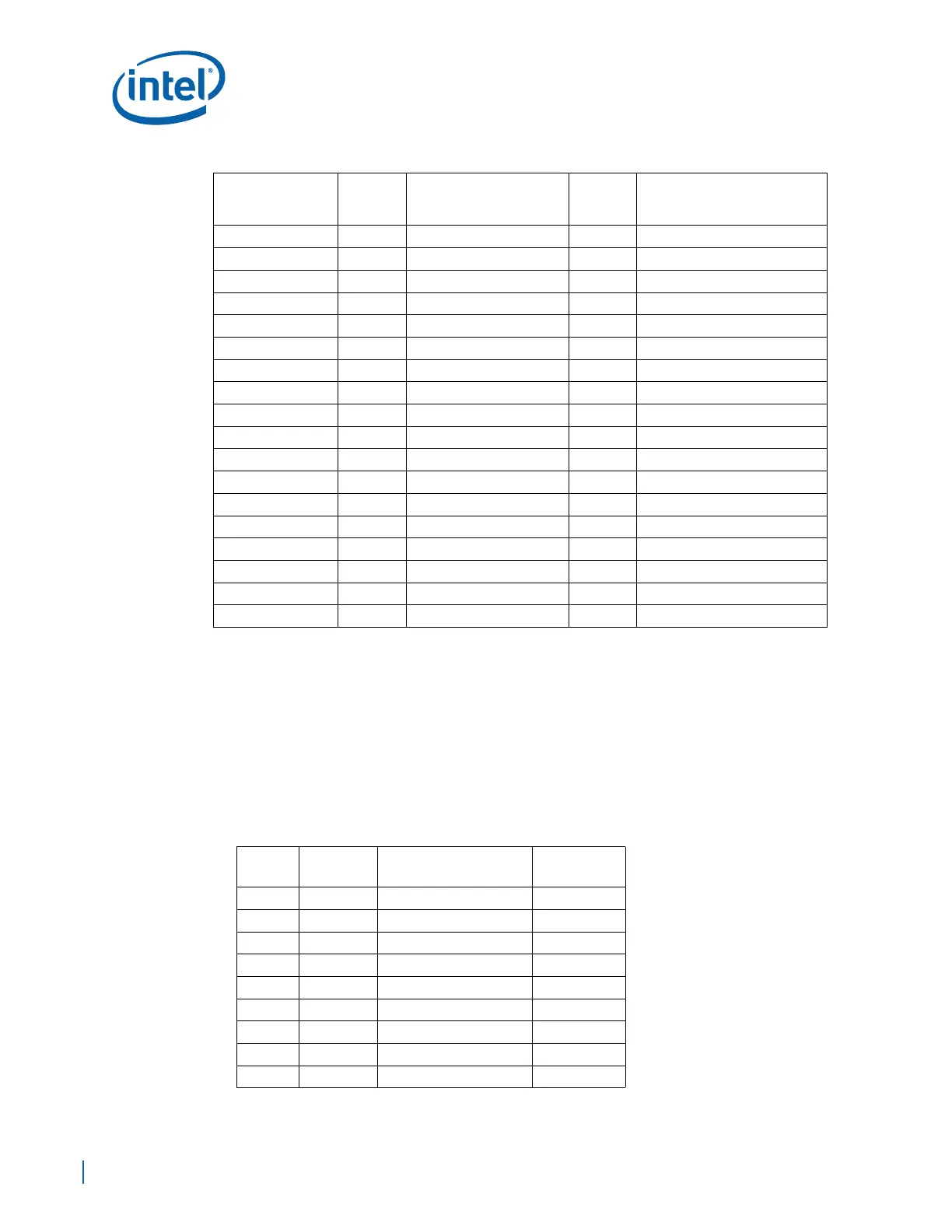

GP18_IRQ36 I T_GPO18_HSS2_INT_N IRQ36 HSS2_INT_N

GP19_IRQ37 I T_GPO19_HSS1_INT_N IRQ37 HSS1_INT_N

GP20_IRQ26 O T_GPO20_SMB_C GPO SMBus_C Enable

GP21_IRQ27 O T_GPO21_SMB_B GPO SMBus_B Enable

GP23_IRQ28 O T_GPO23_SMB_A GPO SMBus_A Enable

GP24_IRQ29 I/O T_GPIO24_FPGA_IO_0 GPIO FPGA_I/O_0

GP25_IRQ38 I/O T_GPIO25_FPGA_IO_1 GPIO FPGA_I/O_1

GP26_SATA0GP I T_GPIO_26_FPGA_IN_11 GPIO FPGA_IN_11

GP27_IRQ39 I/O T_GPIO27_FPGA_IO_2 GPIO FPGA_I/O_2

GP28_IRQ30 I/O T_GPIO28_FPGA_IO_3 GPIO FPGA_I/O_3

GP29_SATA1GP I T_GPIO_29_FPGA_IN_8 GPIO FPGA_IN_8

GP30_IRQ31 I IMCH_SLP_N IRQ31 Sleep signal by External Jumper

GP31_IRQ32 I T_GPI31 GPI Header

GP33_IRQ33 I/O T_GPIO33_FPGA_IO_4 GPIO FPGA_I/O_4/SPI Boot Select

GP34_IRQ34 I/O HPI_GPIO_34 GPIO HSS1 EXT

GP40_IRQ35 I IERR_GPI40 GPI IERR Signal)

LDRQ[1]_N I L_DRQ1_N GPI LPC DMA Request

GPIO[48] O T_GPO_48_FPGA_OUT_5 GPO FPGA_OUT_5

Table 76. Development Board GPIO Usage (Sheet 2 of 2)

Pin Name

I/O

(Default

Mode)

Signal Name

Mode of

Operatio

n

Function

Table 77. Interrupt Configurations - APIC Mode (Sheet 1 of 2)

IRQ #

Interrupt

Name

Source Pin Name

16 PIRQA SERIRQ N/A

17 PIRQB SERIRQ N/A

18 PIRQC SERIRQ N/A

19 PIRQD SERIRQ N/A

20 PIRQE External PIRQE

21 PIRQF External PIRQF

22 PIRQG External PIRQG

23 PIRQH External PIRQH

24 External GPIO[16]

Loading...

Loading...